# Auswirkungen von LDD-Strukturen auf die elektrischen Eigenschaften von MOS-Transistoren

Elmar Gondro

Technische Universität München

Physik-Department

November 1997

# Inhaltsverzeichnis

|                                                               |           |

|---------------------------------------------------------------|-----------|

| <b>1 Einleitung</b>                                           | <b>1</b>  |

| <b>2 Der MOS-Transistor mit Lightly Doped Drain</b>           | <b>4</b>  |

| 2.1 Aufbau und Wirkungsweise . . . . .                        | 4         |

| 2.2 Dotierungsübergänge . . . . .                             | 8         |

| 2.2.1 Der $pn$ -Übergang . . . . .                            | 8         |

| 2.2.2 Der $n^-n^+$ -Übergang . . . . .                        | 13        |

| 2.2.3 Der $pn^-n^+$ -Übergang . . . . .                       | 14        |

| 2.2.4 Diffundierter Übergang . . . . .                        | 15        |

| 2.3 Elektrische Feldstärke . . . . .                          | 17        |

| 2.4 Stoßionisation . . . . .                                  | 20        |

| 2.5 Substratstrom . . . . .                                   | 21        |

| <b>3 Modellierung des MOS-Transistors</b>                     | <b>23</b> |

| 3.1 Widerstandsbereich . . . . .                              | 27        |

| 3.2 Sättigungsbereich . . . . .                               | 29        |

| <b>4 Neues Widerstandsmodell</b>                              | <b>33</b> |

| 4.1 Effektive Kanallänge . . . . .                            | 34        |

| 4.1.1 Bestimmung der effektiven Kanallänge . . . . .          | 37        |

| 4.2 Messungen . . . . .                                       | 39        |

| 4.3 Widerstandsverhalten von Source und Drain . . . . .       | 40        |

| 4.3.1 Extraktionsmethoden . . . . .                           | 41        |

| 4.3.1.1 Widerstandsextraktion durch Iterationsverfahren . . . | 41        |

| 4.3.1.2 Widerstandsextraktion durch Parameteranpassung . .    | 41        |

|                                            |                                                               |           |

|--------------------------------------------|---------------------------------------------------------------|-----------|

| 4.3.2                                      | Modell des Source-Widerstands . . . . .                       | 43        |

| 4.3.3                                      | Der Akkumulationswiderstand . . . . .                         | 44        |

| 4.3.3.1                                    | Poisson-Gleichung . . . . .                                   | 46        |

| 4.3.3.2                                    | Charge sheet-Näherung . . . . .                               | 51        |

| 4.3.4                                      | Der Spreading-Widerstand . . . . .                            | 53        |

| 4.3.4.1                                    | Extraktion des Streuwinkels . . . . .                         | 55        |

| 4.3.5                                      | Parallelschaltung von Akkumulations- und Spreading-Widerstand | 57        |

| 4.3.6                                      | Raumladungszone . . . . .                                     | 60        |

| 4.3.7                                      | Zusammenfassung des Überlappwiderstandes . . . . .            | 61        |

| 4.3.8                                      | Kontakt- und Schichtwiderstand . . . . .                      | 62        |

| 4.3.8.1                                    | Mittlere Dotierung . . . . .                                  | 64        |

| 4.3.8.2                                    | Bildladungsmethode . . . . .                                  | 66        |

| 4.3.9                                      | Vergleich mit bestehenden Modellen . . . . .                  | 70        |

| <b>5</b>                                   | <b>Zusammenfassung</b>                                        | <b>73</b> |

| <b>Liste der verwendeten Formelzeichen</b> |                                                               | <b>75</b> |

| <b>Abbildungsverzeichnis</b>               |                                                               | <b>79</b> |

| <b>Literaturverzeichnis</b>                |                                                               | <b>82</b> |

# Kapitel 1

## Einleitung

Um Produktionskosten und Entwicklungsdauer integrierter Schaltungen im wachsenden Wettbewerb möglichst gering zu halten, wird deren Schaltverhalten vor der Fertigung ausführlich simuliert.

Die dazu benötigten Simulationsmodelle müssen die einzelnen Bauelemente hinreichend genau wiedergeben, zugleich aber möglichst einfach sein, um komplexe Schaltungen in akzeptabler Zeit simulieren zu können.

Es existieren im wesentlichen drei Ansätze, derartige Modelle zu konzeptionieren: *Empirische Modelle* bilden die gemessenen Charakteristika durch beliebige Funktionen nach. Vorteilhaft ist die hohe Geschwindigkeit, wohingegen solche Modelle nur unter den gemessenen Randbedingungen aussagekräftig sind.

In *Tabellenmodellen* werden aus den Meßdaten, wie der Name schon sagt, große Tabellen angelegt und die gesuchten Größen durch Interpolation ermittelt. Dies kann bei großer Dimensionalität der Tabelle jedoch recht aufwendig werden; außerdem ist es auch bei dieser Methode nicht möglich, Vorhersagen für Technologieänderungen zu treffen.

Im Gegensatz zu den bisher genannten Vorgehensweisen basieren *Kompaktmodelle* auf physikalischen Annahmen und versuchen, das komplexe elektrische Verhalten der Bauelemente in möglichst einfachen analytischen Gleichungen zu subsumieren. Dies hat den Vorteil, daß das Schaltverhalten der Bauteile auch für zukünftige Technologien ermittelbar ist und soll Zielrichtung dieser Arbeit sein.

Das zentrale Bauteil der Halbleiterbauelemente ist der *Feldeffekttransistor*. Dessen Schaltverhalten wird durch den Kanalbereich bestimmt, der bereits mannigfach unter-

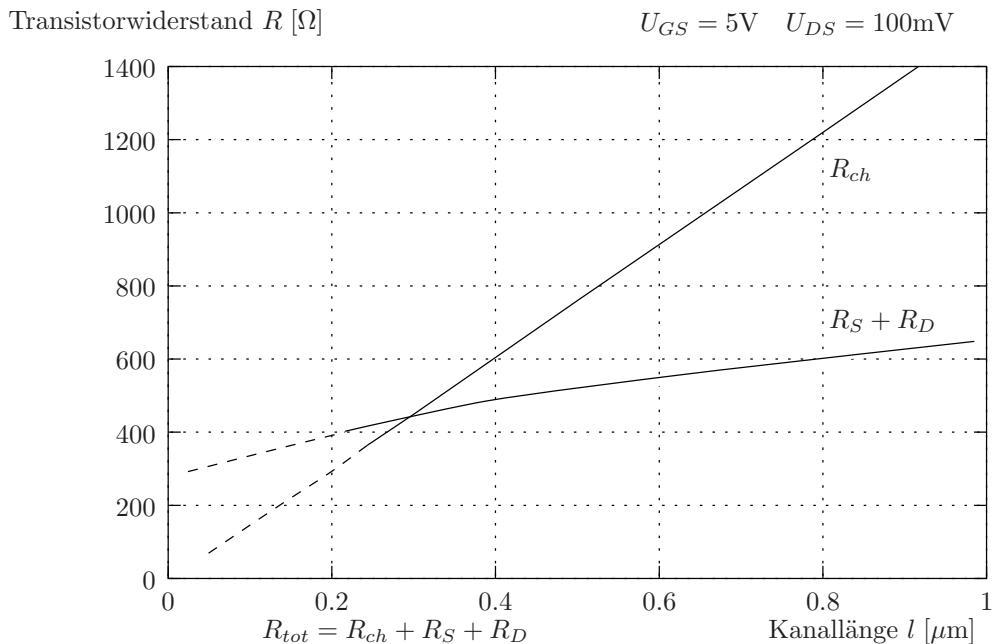

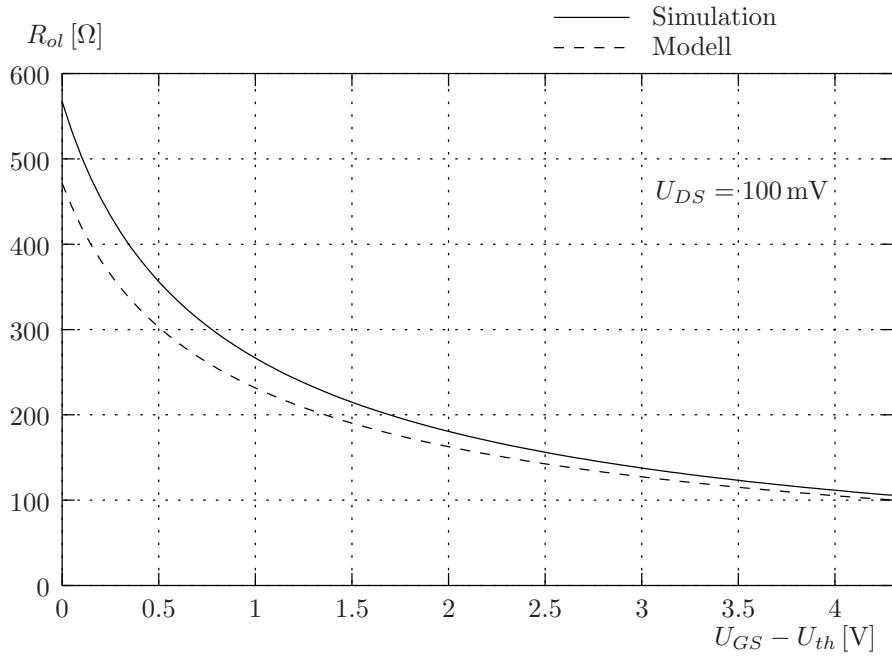

sucht wurde. Die immer weiter fortschreitende Miniaturisierung im Schaltungs-Design — und somit auch der Bauelementgeometrie – stellen immer neue Anforderungen an die Modelle. So erscheint beispielsweise die auf den Kanalbereich reduzierte Betrachtung des Feldeffekttransistors als unzureichend; diese muß auch auf den „äußeren Transistor“, der sich von der Kontaktierung bis zum Kanalbeginn erstreckt, erweitert werden. Dies ist umso bedeutsamer, da dieser Bereich nicht in gleichem Maße skaliertbar ist wie der innere Transistor [10]. Mithin erreicht der externe Widerstand ab einer Kanallänge von etwa  $0,3 \mu\text{m}$  sogar die gleiche Größenordnung wie der Kanalwiderstand (Abb. 1.1).

Abbildung 1.1: Vergleich zwischen Kanal- und externem Widerstand für verschiedene Kanallängen

Er bedarf daher einer fundierten Betrachtung. Diese ist besonders bedeutsam für die heutzutage vorrangigen Transistoren mit *Lightly Doped Drain*, da deren externer Widerstand nicht konstant, sondern vor allem im Überlappgebiet spannungsabhängig ist.

Bestehende Kompaktmodelle beschreiben gewöhnlich die Gate-Spannungs-Abhängigkeit der LDD-Gebiete durch eine spannungsabhängige *effektive Kanallänge*. Diese dehnt lediglich die Beschreibung des inneren Transistors auf die äußeren Gebiete aus.

Wünschenswert wäre jedoch eine, auf geometrischen Größen basierende, separate Betrachtung des äußeren und inneren Transistors. Um MOS-Transistoren mit Hilfe der

geometrischen Kanallänge (Abstand der  $pn$ -Übergänge) modellieren zu können, ist es notwendig, die Leitfähigkeit der LDD-Gebiete analytisch zu beschreiben.

In dieser Diplomarbeit soll mittels des 2D-Simulators MEDICI (TMA) der Einfluß der LDD-Gebiete auf das elektrische Feld sowie auf Stoßionisation und Substratstrom untersucht werden. Darauf aufbauend wird ein *analytisches Modell des äußeren Transistors* entwickelt, das gänzlich auf unphysikalische Fit-Größen verzichtet und nur auf Geometrie- und Dotierungsdaten basiert.

# Kapitel 2

## Der MOS-Transistor mit Lightly Doped Drain

### 2.1 Aufbau und Wirkungsweise

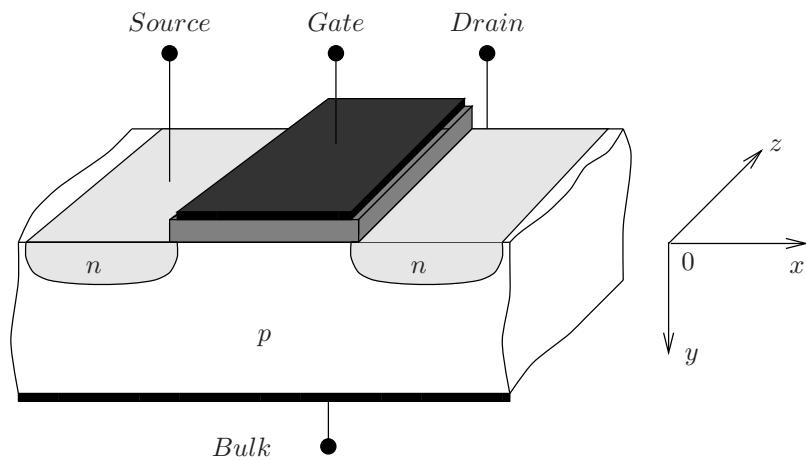

Die Bezeichnung MOSFET ist ein Akronym für *metal-oxide semiconductor field-effect transistor*. Abbildung 2.1 zeigt dessen prinzipielle Struktur.

Abbildung 2.1: MOS-Feldeffekt-Transistor

Auf ein *p*-dotiertes Substrat werden zwei hochdotierte *n*-Gebiete implantiert, die man *Source* und *Drain* nennt. Oberhalb des Bereiches zwischen diesen beiden Kontakten

wird, abgegrenzt durch eine dünne isolierende Siliziumdioxidschicht, die Steuerelektrode (*Gate*) aufgebracht. Diese kann aus Metall bestehen, woher die Bezeichnung MOS röhrt, wird heutzutage aber aus hochdotiertem Polysilizium oder Polyzid hergestellt. Meist wird auch das Substrat, englisch *Bulk*, kontaktiert, so daß der konventionelle MOSFET eine Vier-Terminal-Struktur darstellt.

Die Potentialdifferenz zwischen Source und Bulk sowie zwischen Drain und Bulk werden stets größer oder gleich Null gewählt, so daß die beiden *pn*-Übergänge in Sperrrichtung gepolt sind. Legt man nun eine positive Spannung zwischen Gate und Bulk, so wird das Potential an der Halbleiteroberfläche über die Sperrspannung der *pn*-Übergänge angehoben und Elektronen von den *n*-Gebieten in das *p*-Substrat injiziert. Die influenzierte Schicht aus Elektronen bildet einen elektrisch leitenden Kanal zwischen Source und Drain. Legt man zwischen diesen beiden Kontakten eine Spannung an, so kann entlang der Halbleiteroberfläche ein Strom fließen, der durch Absenken des Gate-Potentials wieder ausgeschaltet werden kann. Im Gegensatz zu einem Bipolar-Transistor, bei dem die Sperrpolung der *pn*-Übergänge durch Injektion von Ladungen aus der Steuerelektrode aufgehoben wird, beruht die Schalt- und Verstärkungswirkung des MOSFETs auf der stromlosen Influenz des elektrischen Feldes zwischen Gate und Bulk; daher der Name FET. Der obig beschriebene Transistortyp wird auch *n*-Kanal- oder kurz NMOS-Transistor genannt. Damit unterscheidet man ihn von einem PMOS-Transistor, bei dem *p*-dotierte Source und Drain in ein *n*-Substrat eingebettet sind und folglich der Kanal aus Löchern gebildet wird. Da dessen Modellgleichungen aber vereinfacht durch einen Vorzeichenwechsel in der Ladung und durch Berücksichtigung der geringeren Beweglichkeit der Löcher aus den Gleichungen für den NMOS hergeleitet werden können, soll er im folgenden unberücksichtigt bleiben. Oftmals wird der PMOS-Transistor als Verarmungs- oder *Depletion*-Transistor eingesetzt.

Abweichend von der konventionellen Form weist ein LDD(S)-MOSFET eine leicht modifizierte Struktur auf. LDD(S) steht für *Lightly Doped Drain (Source)*.

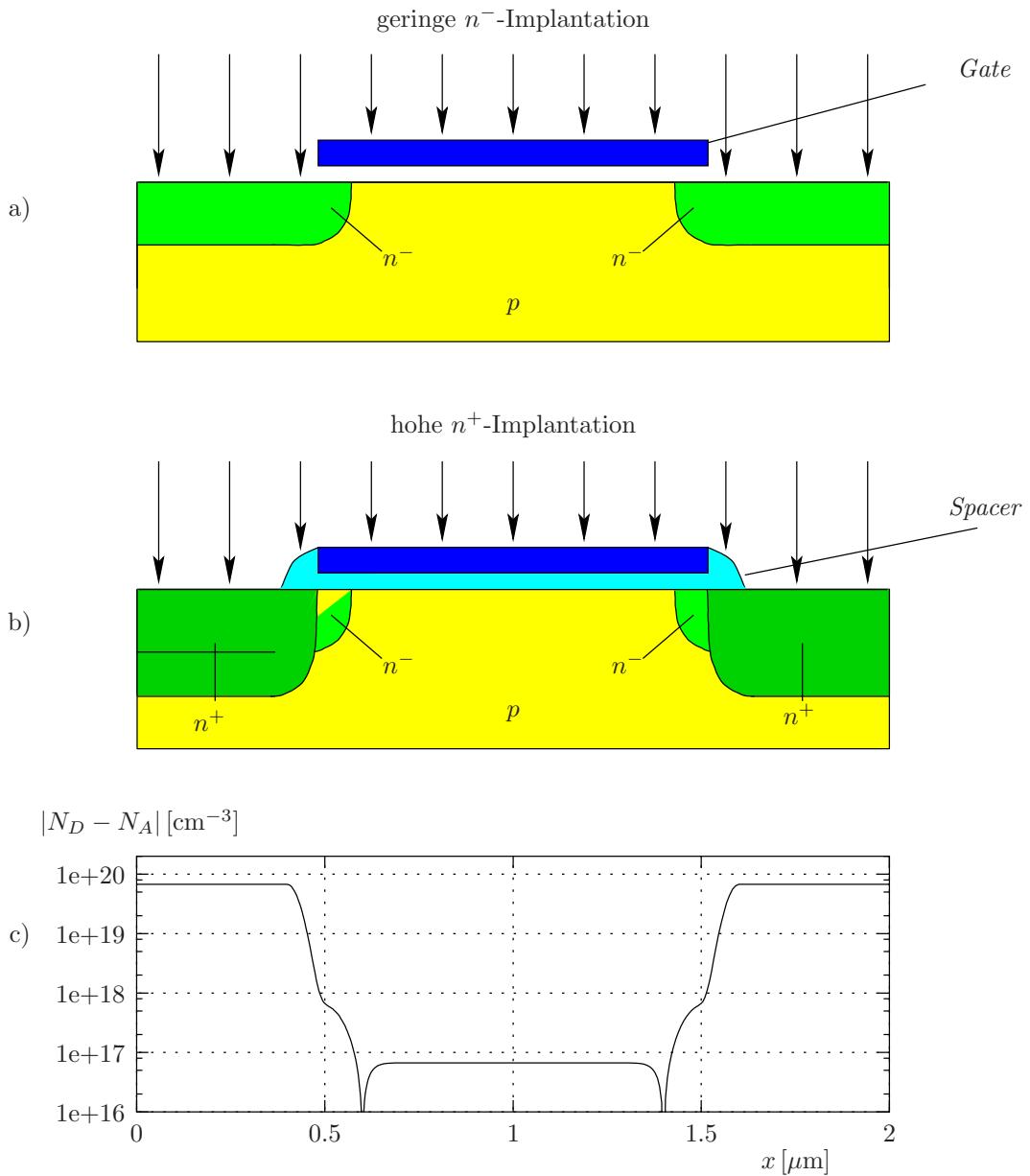

Hierbei herrscht im Ausdiffusionsgebiet unter dem Gate (*overlap*) eine niedrigere Dotierung vor als direkt unter der Source und der Drain. Um eine solche Struktur zu erhalten, sind zusätzliche Technologieschritte vonnöten, deren Prinzip aus Abbildung 2.2 ersichtlich ist.

Das über dem Oxid aufgebrachte Gate wirkt bei der geringen Donatoren-Implantation als selbstjustierende Maske. Hierdurch wird eine hohe Symmetrie der drain- und source-seitigen Überlappgebiete erreicht. Nach Aufoxidation von sogenannten *Spacern* bildet

Abbildung 2.2: Herstellung eines MOSFETs mit *Lightly Doped Drain*

- a) an der Gatekante selbstjustierende  $n^-$ -Implantation

- b)  $n^+$ -Implantation nach vorheriger Spacer-Oxidation

- c) Typisches Dotierungsprofil an der Halbleiteroberfläche

man in einem zweiten Implantierungsschritt die nach außen versetzten hochdotierten Gebiete. Ergänzend sei noch erwähnt, daß die Ausdehnung der  $n^-$ -Gebiete mitunter auch in vertikaler Richtung die der hochdotierten Gebiete übertrifft, damit mögliche Substratdurchbrüche vermieden werden.

Worin liegt nun aber der Sinn dieses zusätzlichen Technologieschrittes?

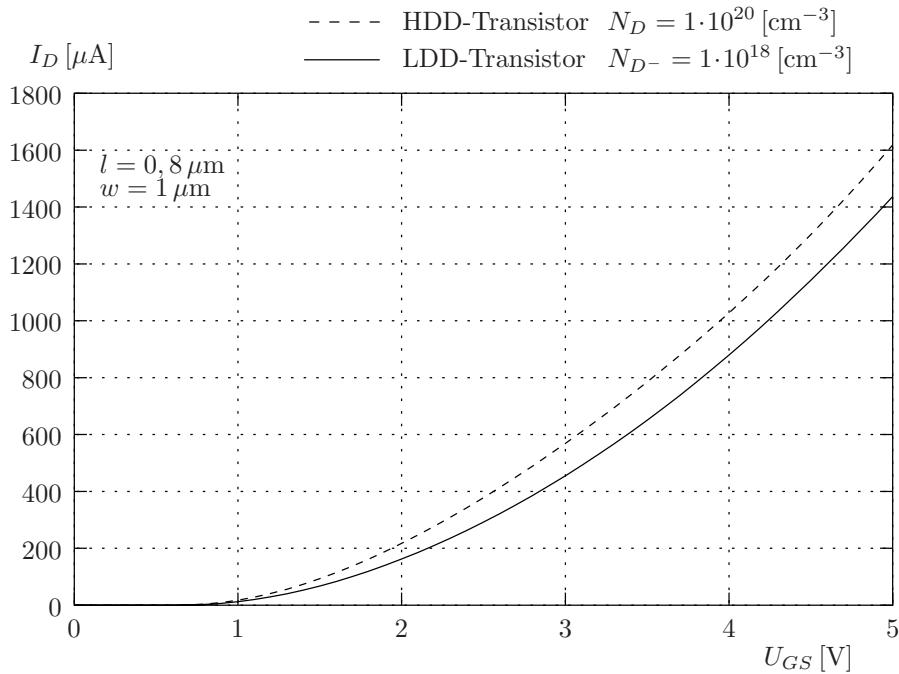

Dieser erscheint zunächst recht ungewöhnlich, wird doch durch die niedrige Leitfähigkeit der  $n$ -Gebiete der Widerstand des Transistors erhöht, was eine verminderte Stromergiebigkeit zur Folge hat (Abbildung 2.3). Außerdem bedeuten mehr Prozeßschritte natürlich höhere Produktionskosten.

Abbildung 2.3: Simulierte Eingangskennlinien eines konventionellen HDD-Transistors und eines LDD-Transistors

Auf der anderen Seite ist es möglich, die hochdotierten Gebiete tiefer ins Substrat hinein zu implantieren. Dies verringert sowohl den Schicht-, als auch den Kontaktwiderstand an Source und Drain. Des weiteren erleichtert eine tiefe Dotierung die Herstellung der Kontakte zu den sich anschließenden Aluminium-Leiterbahnen [25].

Der gewichtigste Grund für die Verwendung von LDD-Transistoren liegt jedoch in der zunehmenden Miniaturisierung der Halbleiterbauelemente. Da die Versorgungsspannung nicht beliebig reduziert werden kann, sind technologische Änderungen notwendig, um bei kleineren Geometrien hohe elektrische Felder zu vermeiden. Diese haben das Auftreten von „heißen Ladungsträgern“ zur Folge, die die Lebensdauer von Bauelementen drastisch verkürzen können [26].

Niedrig dotierte Strukturen bieten hier die Möglichkeit, die „innere“ Versorgungsspannung anzupassen. Sie wirken dann wie ein externer Serienwiderstand.

Zum anderen lassen sich damit hohe elektrische Feldstärken reduzieren. Dieses soll in den folgenden Kapiteln anhand der metallurgischen Übergänge verdeutlicht werden.

## 2.2 Dotierungsübergänge

Betrachtet man die Drain-Struktur in der Nähe der Halbleiteroberfläche, so lässt diese sich für einen konventionellen Transistor auf einen  $pn$ -Übergang reduzieren. Ein LDD-Transistor hingegen wird durch einen  $pn^-n^+$ -Übergang charakterisiert.

### 2.2.1 Der $pn$ -Übergang

Zunächst soll nun der einfache  $pn$ -Übergang untersucht werden. Zur Vereinfachung seien homogene Dotierungen und damit abrupte Übergänge angenommen. An der Schnittstelle der  $p$ - und  $n$ -dotierten Gebiete stehen sich unterschiedliche Konzentrationen von Elektronen ( $n$ ) und Löchern ( $p$ ) gegenüber. Infolgedessen diffundieren Löcher in das  $n$ -Gebiet sowie Elektronen in das  $p$ -Gebiet. Die nicht mehr voll kompensierten Akzeptor- und Donatorionen ( $N_A^-$  und  $N_D^+$ ) verursachen eine elektrisches Feld. Dieses hat Driftströme der Löcher und Elektronen zur Folge, welche im thermodynamischen Gleichgewicht die Diffusionsströme gerade kompensieren ( $\vec{j}_{diff} = -\vec{j}_{drift}$ ). Ohne anliegende äußere Spannungen verschwindet daher der Nettostrom. Die einzelnen Stromdichten kann man folgendermaßen ausdrücken:

$$\vec{j}_{diff} = qD_n \vec{\nabla}n - qD_p \vec{\nabla}p \quad (2.1)$$

$$\vec{j}_{drift} = -q\vec{E}\mu_n n + q\vec{E}\mu_p p \quad (2.2)$$

Mit den Einstein-Beziehungen lassen sich die Diffusionskonstanten  $D_{p,n}$  durch die entsprechenden Beweglichkeiten  $\mu_{p,n}$  beschreiben.

$$D_p = \frac{kT}{q}\mu_p \quad D_n = \frac{kT}{q}\mu_n \quad (2.3)$$

- $k$ : Boltzmann-Konstante

- $q$ : Elementarladung

- $T$ : Temperatur in Kelvin

Der Nettostrom verschwindet auch bei getrennter Betrachtung von Elektronen- respektive Löcherströmen.

$$\begin{aligned}\vec{j}_p &= \underbrace{qp\mu_p \vec{E}}_{\text{Drift}} - \underbrace{qD_p \vec{\nabla} p}_{\text{Diffusion}} = 0 \\ \vec{j}_n &= \underbrace{qn\mu_n \vec{E}}_{\text{Drift}} + \underbrace{qD_n \vec{\nabla} n}_{\text{Diffusion}} = 0\end{aligned}\quad (2.4)$$

Aus  $\vec{j}_n = 0$  folgt

$$\vec{E} = -\frac{D_n}{\mu_n n} \vec{\nabla} n \quad (2.5)$$

und damit die über den  $pn$ -Übergang abfallende Diffusionsspannung  $\phi_i$ .

$$\phi_i = - \int_{x_p}^{x_n} E dx \stackrel{(2.3)}{=} \frac{kT}{q} \int_{n(x_p)}^{n(x_n)} \frac{dn}{n} = \frac{kT}{q} \ln \frac{n(x_n)}{n(x_p)} = \phi_t \ln \frac{n(x_n)}{n(x_p)} \quad (2.6)$$

Entsprechend resultiert  $\phi_i = \phi_t \ln \frac{p(x_n)}{p(-x_p)}$  aus  $\vec{j}_p = 0$ . Mit  $\phi_t$  bezeichnet man die *Thermospannung*. Sie liegt unter Normalbedingungen bei 26 mV.

Zur weiteren Auswertung obiger Gleichung benötigt man die Ladungsträgerdichten eines Halbleiters im thermodynamischen Gleichgewicht. Man erhält sie durch Multiplikation der Zustandsdichten mit der Fermi-Besetzungs wahrscheinlichkeit und anschließender Integration über das Leitungsband.

$$n = N_c e^{-\frac{E_c - E_F}{kT}} \quad (2.7)$$

$$p = N_v e^{-\frac{E_F - E_v}{kT}} \quad (2.8)$$

Darin bedeuten  $N_c$  und  $N_v$  die effektiven Zustandsdichten im Leitungsband (Energie niveau  $E_c$ ) und Valenzband (Energieniveau  $E_v$ ).  $E_F$  bezeichnet das Fermi-Niveau und liegt im undotierten (intrinsischen) Halbleiter etwa in der Mitte zwischen  $E_c$  und  $E_v$ . Multiplikation beider Gleichungen führt zum *Massenwirkungsgesetz*:

$$n p = N_c N_v e^{-\frac{E_c - E_v}{kT}} = N_c N_v e^{-\frac{E_g}{kT}} = n_i^2 \quad (2.9)$$

Hierin steht  $n_i$  für die *Intrinsic-Dichte*, die Konzentration der Elektronen und Löcher in einem undotierten Halbleiter. Die Differenz von Leitungsbandkante  $E_c$  und Valenzbandkante  $E_v$  ist der Bandabstand  $E_g$ . Beide Größen sind material- und temperaturabhängig und betragen bei Raumtemperatur (300 K) in Silizium  $1,45 \cdot 10^{10} \text{ cm}^{-3}$  und 1,12 eV. Aus den Gleichungen (2.7) und (2.8) kann man ablesen, daß das Fermi-Niveau

in einem undotierten Halbleiter ( $n_0 = p_0, E_F = E_i$ ) in etwa mittig im unbesetzten Bereich zwischen Leitungs- und Valenzbandkante liegt.

$$E_i = E_{F_{intrinsic}} = \frac{E_c - E_v}{2} + \frac{kT}{2} \ln \frac{N_v}{N_c} \quad (2.10)$$

Mit (2.9) lassen sich die Ladungsträgerkonzentrationen dann auch folgendermaßen ausdrücken:

$$n = n_i e^{-\frac{E_F - E_i}{kT}} = n_i e^{\frac{q\psi}{kT}} \quad (2.11)$$

$$p = n_i e^{-\frac{E_i - E_F}{kT}} = n_i e^{-\frac{q\psi}{kT}} \quad (2.12)$$

Diese Gleichungen besagen, daß eine Variation des Fermi-Niveaus von seinem intrinsischen Wert eine exponentielle Variation der Ladungsträgerdichten mit sich führt.

Oberhalb einer Temperatur von etwa 100 K sind die Dotieratome fast vollständig ionisiert [6].

$$N_A^- \approx N_A \quad N_D^+ \approx N_D \quad (2.13)$$

Die Ladungsneutralität in einem Halbleiter läßt sich dann folgendermaßen ausdrücken:

$$-q n + q N_D + q p - q N_A = 0 \quad (2.14)$$

Für einen  $n$ -Typ Halbleiter ( $N_D \gg N_A$ ) vereinfachen sich die vorhergehenden Gleichungen mit (2.9) zu

$$n \approx N_D \quad p \approx \frac{n_i^2}{N_D} \quad (2.15)$$

und für einen  $p$ -Typ Halbleiter ( $N_A \gg N_D$ ) zu:

$$p \approx N_A \quad n \approx \frac{n_i^2}{N_A} \quad (2.16)$$

Jetzt kann man Gleichung (2.6) weiter auswerten und für den Spannungsabfall über den  $pn$ -Übergang schreiben:

$$\phi_i = \phi_t \ln \frac{N_D}{n_i^2/N_A} = \phi_t \ln \frac{N_D N_A}{n_i^2} \quad (2.17)$$

Da das  $n^-$ -Gebiet in der Regel um zwei bis drei Größenordnungen niedriger dotiert ist als das  $n^+$ -Gebiet (siehe Abbildung 2.5), ersieht man des weiteren, daß der Potentialabfall an der metallurgischen Grenze des  $pn^-$ -Übergangs etwa 20-fach niedriger

ausfällt als bei einem reinen  $pn^+$ -Übergang. Für  $N_A = 10^{17} \text{ cm}^{-3}$ ,  $N_{D^-} = 5 \cdot 10^{17} \text{ cm}^{-3}$  und  $N_{D^+} = 10^{20} \text{ cm}^{-3}$  erhält man  $\phi_i \approx 1000 \text{ mV}$  für den  $pn^+$ -Übergang sowie  $\phi_i \approx 860 \text{ mV}$  für den  $pn^-$ -Übergang.

Die Poisson-Gleichung beschreibt das durch eine Ladungsverteilung  $\varrho$  hervorgerufene Feld; sie entspricht der ersten Maxwell-Gleichung:

$$\varepsilon_0 \varepsilon_{si} \vec{\nabla}^2 \psi = -\varrho \quad (2.18)$$

Für die Raumladungszone kann in guter Näherung angenommen werden, daß eine vollständige Verarmung an beweglichen Ladungsträgern vorliegt (*Depletion-Näherung*). Die Poisson-Gleichung lässt sich dann für das  $p$ -Gebiet zu

$$\vec{\nabla}^2 \psi = -\frac{qN_A}{\varepsilon_0 \varepsilon_{si}} \quad (2.19)$$

und für das  $n$ -Gebiet zu

$$\vec{\nabla}^2 \psi = +\frac{qN_D}{\varepsilon_0 \varepsilon_{si}} \quad (2.20)$$

vereinfachen. Da das elektrische Feld  $E$  dem negativen Gradienten des Potentials  $\psi$  entspricht, folgt durch Integration über den Ort ein linearer Feldverlauf.

$$E(x) = \begin{cases} -\frac{qN_A}{\varepsilon_0 \varepsilon_{si}} (x + x_p) & : -x_p \leq x \leq 0 \\ E(x=0) + \frac{qN_D}{\varepsilon_0 \varepsilon_{si}} x = -\frac{qN_A}{\varepsilon_0 \varepsilon_{si}} x_p + \frac{qN_D}{\varepsilon_0 \varepsilon_{si}} x & : 0 < x \leq x_n \\ 0 & : \text{sonst} \end{cases} \quad (2.21)$$

Dabei erstreckt sich die Raumladungszone von  $-x_p$  im  $p$ -Gebiet bis  $x_n$  im  $n$ -Gebiet und hat eine Weite von:

$$\omega = x_n + x_p \quad (2.22)$$

Für die metallurgische Grenze wird  $x = 0$  gesetzt. Dies ist der Ort der größten Feldstärke.

Aufgrund der Ladungsneutralität der Raumladungszone gilt

$$N_A \cdot x_p = N_D \cdot x_n \quad (2.23)$$

und somit:

$$E(x=0) = \frac{qN_A}{\varepsilon_0 \varepsilon_{si}} \cdot x_p = \frac{qN_D}{\varepsilon_0 \varepsilon_{si}} \cdot x_n \quad (2.24)$$

Letzteres besagt, daß die Weite der Raumladungszone maßgeblich durch die geringer dotierte Seite des  $pn$ -Übergangs bestimmt wird.

Legt man ferner eine äußere Spannung  $U$  an den Übergang, die von der  $n$ - zur  $p$ -Region und somit in Sperrichtung gepolt ist, so muß gelten:

$$U + \phi_i = - \int_{x \rightarrow -\infty}^{x \rightarrow \infty} E dx \quad (2.25)$$

Die Fläche unter der Feldstärke entspricht ergo der an der Raumladungszone wirksamen Spannung. Vernachlässigt man den Spannungsabfall außerhalb der Raumladungszone, so folgt mit (2.21) und (2.22):

$$U + \phi_i = - \frac{1}{2} E(x=0) \cdot \omega \quad (2.26)$$

$$\omega = -2 \frac{U + \phi_i}{E(x=0)} \quad (2.27)$$

Eine weitere Bestimmungsgleichung für die Raumladungszonenweite ergibt sich aus (2.22) bis (2.23).

$$\omega = -2 \frac{\varepsilon_0 \varepsilon_{si}}{q} E(x=0) \left( \frac{1}{N_A} + \frac{1}{N_D} \right) \quad (2.28)$$

Multipliziert man die letzten beiden Gleichungen und zieht die Wurzel, so erhält man  $\omega$  als Funktion der Spannung und der Dotierungen.

$$\begin{aligned} \omega &= \sqrt{2 \frac{\varepsilon_0 \varepsilon_{si}}{q} (U + \phi_i) \left( \frac{1}{N_A} + \frac{1}{N_D} \right)} \\ &\stackrel{(2.17)}{=} \sqrt{2 \frac{\varepsilon_0 \varepsilon_{si}}{q} \left( U + \phi_t \ln \frac{N_A N_D}{n_i^2} \right) \left( \frac{1}{N_A} + \frac{1}{N_D} \right)} \end{aligned} \quad (2.29)$$

Für die maximale Feldstärke folgt

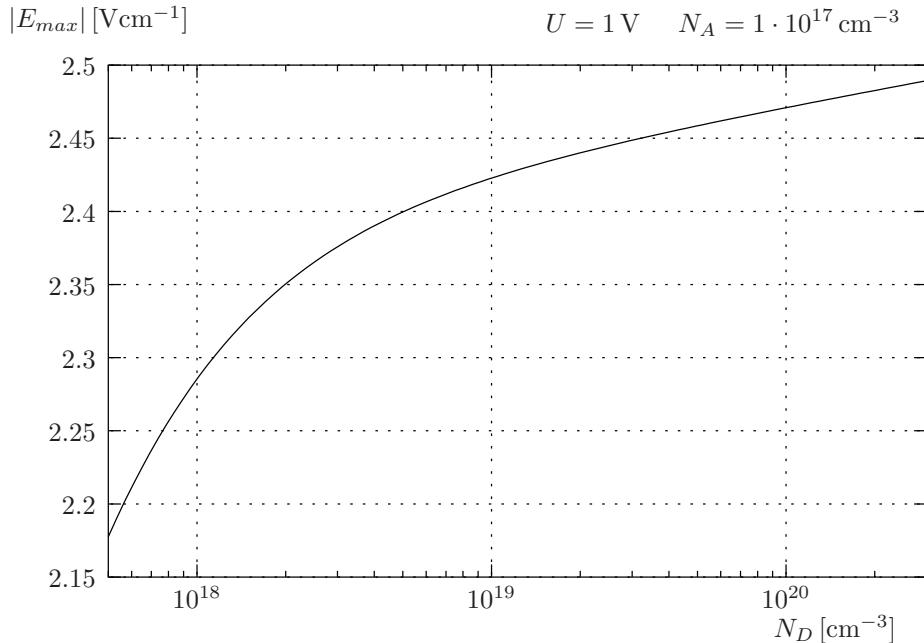

$$\begin{aligned} E_{max} &= E(x=0) \\ &= -2 (U + \phi_i) \cdot \frac{1}{\sqrt{2 \frac{\varepsilon_0 \varepsilon_{si}}{q} (U + \phi_i) \left( \frac{1}{N_A} + \frac{1}{N_D} \right)}} \\ &= -\sqrt{\frac{2 q}{\varepsilon_0 \varepsilon_{si}} \left( U + \phi_t \ln \frac{N_A N_D}{n_i^2} \right) \left( \frac{N_A \cdot N_D}{N_A + N_D} \right)} \end{aligned} \quad (2.30)$$

Abbildung 2.4 zeigt den analytischen Verlauf von  $E_{max}$  für eine Spannung von  $U = 1 \text{ V}$  und eine Akzeptorkonzentration  $N_A = 10^{17} \text{ cm}^{-3}$ . Diese entspricht im NMOS der Substratdotierung und die Donatorenkonzentration  $N_D$  der Source/Drain-Dotierung.

Abbildung 2.4: Analytische Abhängigkeit der maximalen Feldstärke am  $pn$ -Übergang in Abhängigkeit von der Donatorenkonzentration

Will man also die maximale Feldstärke unter einem kritischen Wert halten, so muß die  $n$ -Dotierung entsprechend gering gehalten werden. Dies genau ist der Sinn einer LDD-Struktur!

## 2.2.2 Der $n^-n^+$ -Übergang

Der Vollständigkeit halber sei nun der  $n^-n^+$ -Übergang betrachtet.

Auch dort herrscht ein Konzentrationsgefälle, welches eine Elektronenwanderung vom  $n^+$ - in das  $n^-$ -Gebiet und somit eine (kleine) Raumladungszone verursacht. Analog zum  $pn$ -Übergang läßt sich die Diffusionsspannung des Übergangs aus der Integration der Transportgleichung (2.4) berechnen. Man kann Gleichung (2.6) direkt anwenden

und findet einen etwas anderen Term als (2.17):

$$\phi_i = \frac{kT}{q} \int_{n^-}^{n^+} \frac{dn}{n} \approx \phi_t \ln \frac{N_{D^+}}{N_{D^-}} \quad (2.31)$$

Mit den im letzten Abschnitt verwendeten Dotierungswerten ergibt sich eine Diffusionsspannung  $U_D \approx 140 \text{ mV}$ , die deutlich geringer als die des  $pn^-$ -Übergangs ausfällt. Entsprechend der Herleitung für den  $pn$ -Übergang ergibt sich für die maximale Feldstärke am  $n^-n^+$ -Übergang:

$$E_{max} = -\sqrt{\frac{2q}{\varepsilon_0 \varepsilon_{si}} \left( U + \phi_t \ln \frac{N_{D^+}}{N_{D^-}} \right) \left( \frac{N_{D^-} \cdot N_{D^+}}{N_{D^-} + N_{D^+}} \right)} \quad (2.32)$$

Sie bleibt selbst bei großen Spannungen ( $U \leq 5 \text{ V}$ ) unter  $900 \text{ Vcm}^{-1}$ , was weit unter der für den Durchbruch kritischen Feldstärke ( $E_{crit} \approx 10^6 \text{ Vcm}^{-1}$  [23]) liegt.

### 2.2.3 Der $pn^-n^+$ -Übergang

Fügt man nun die  $pn^-$ - und die  $n^-n^+$ -Strukturen zusammen, so erhält man das Pendant zu einer LDD-Struktur. Die gesamte Diffusionsspannung lässt sich durch Summation der Spannungen am  $pn^-$ -Übergang (Gleichung 2.17) und am  $n^-n^+$ -Übergang (Gleichung 2.31) berechnen. Beide Komponenten tragen gleiches Vorzeichen.

$$\begin{aligned} \phi_i &= \phi_{i_{pn^-}} + \phi_{i_{n^-n^+}} \\ &= \phi_t \ln \frac{N_A N_{D^-}}{n_i^2} + \phi_t \ln \frac{N_{D^+}}{N_{D^-}} \\ &= \phi_t \ln \frac{N_A N_{D^+}}{n_i^2} \end{aligned} \quad (2.33)$$

Die über die LDD-Struktur abfallende Diffusionsspannung ist also unabhängig von der  $N_{D^-}$ -Dotierung und entspricht somit dem Spannungsabfall bei einem konventionellen Transistor!

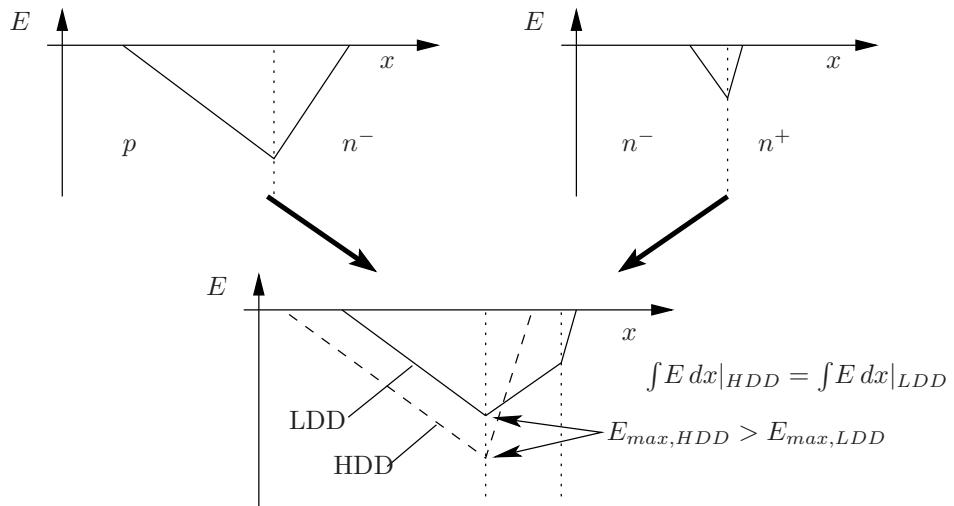

Zusammenfassend lässt sich sagen, daß die Feldminderung beim LDD-Transistor auf zwei Effekten beruht: zum einen wird ein Teil des Spannungsfalls auf den  $n^-n^+$ -Übergang verlagert, zum anderen fällt die Spannung wegen der größeren  $pn^-$ -Raumladungszone über einen ausgedehnteren Bereich ab. Voraussetzung für die Richtigkeit obiger Herleitung ist, daß die beiden Raumladungszonen keinen

wechselseitigen Einfluß ausüben, das  $n^-$ -Gebiet also hinreichend groß ist.

Verjüngt man hingegen den schwach  $n$ -dotierten Bereich, so kommt es zu einer Überlagerung der Raumladungszonen. Man verläßt dann den Gültigkeitsbereich der *Depletion*-Näherung, da die injizierten Elektronen die positiven Donatorrümpfe im  $n^-$ -Bereich teilweise kompensieren. Linearisiert man den Ladungsverlauf im Überlappgebiet und beachtet, daß das Integral über die Feldstärke auch dann gleich der Summe aus Diffusions- und außen anliegender Spannung sein muß, so erhält man nachstehend skizzierte Verläufe.

Abbildung 2.5: Verlauf der Feldstärke am  $pn^-n^+$ -Übergang im Vergleich zum  $pn$ -Übergang bei *Depletion*-Näherung (vgl. Abb. 2.7)

## 2.2.4 Diffundierter Übergang

Die bisherigen Überlegungen galten für abrupte Übergänge der Dotierungen. In der Praxis führt die Diffusion der Dotieratome bei der Herstellung zu graduellen Profilen. Deren Ausbildung hängt stark von der Temperatur und der Zeitdauer des Diffusionsprozesses ab.

Sieht man von Transistoren mit *pocket implantation* ab, so kann man für einen  $n$ -Kanäler ein konstant dotiertes Substrat annehmen. Die Verteilung der Donatoratome im Randbereich von Source und Drain läßt sich mit der Diffusionsgleichung beschreiben [24].

Ist die Quelle der Dotieratome unbegrenzt, ergibt sich als Lösung die komplementäre Errorfunktion.

$$N_D(x) = N_{D_0} \operatorname{erfc}\left(\frac{x}{\lambda}\right) \quad (2.34)$$

Erfolgt die Diffusion hingegen aus einer begrenzten Dotandenquelle, so erhält man ein gaußförmiges Dotierungsprofil.

$$N_D(x) = N_{D_0} \exp\left(-\frac{x^2}{\lambda^2}\right) \quad (2.35)$$

Die charakteristische Diffusionslänge  $\lambda$  nimmt mit der Temperatur und der Dauer der Ausheizung zu. Im folgenden sei letztere Profilvariante angenommen, da in den Device-Simulationen mit MEDICI die Dotierungsprofile gaußförmig implementiert wurden.

Die in den vorangegangen Kapiteln durchgeführte Berechnung der Feldstärke und Ladungsträgerverteilung ist für diffundierte Übergänge nur bedingt anwendbar, da in Bereichen starker Dotierungsänderung die Zunahme an Elektronen nicht mit der Abnahme an Löchern korreliert und mithin die *Depletion*-Näherung sehr ungenau wird. Der Gradient der Donatorkonzentration hat ein „eingebautes“ elektrisches Feld zur Folge, welches sich entsprechend der Gleichung (2.5) beschreiben lässt:

$$\vec{E} = -\frac{D_n}{\mu_n N} \vec{\nabla} N \stackrel{(2.3)}{=} \phi_t \frac{1}{N} \vec{\nabla} N \quad (2.36)$$

Es verursacht eine Verschiebung des Feldstärkemaximums von der metallurgischen Grenze in das Diffusionsgebiet. Diese fällt umso stärker aus, je „weicher“ das Profil gebildet wird.

Die räumliche Potential- und Feldverteilung wird durch die Poisson-Gleichung (2.18) bestimmt. Für das diffundierte  $n$ -Gebiet ergibt sich:

$$-\varepsilon_0 \varepsilon_{si} \vec{\nabla}^2 \psi = q [-n(x) + p(x) + N_D(x) - N_A] \quad (2.37)$$

$$\text{mit } n(x) \stackrel{(2.11)}{=} n_i e^{+\frac{q}{kT} \psi(x)} \quad (2.38)$$

$$p(x) \stackrel{(2.12)}{=} n_i e^{-\frac{q}{kT} \psi(x)} \quad (2.39)$$

$$N_D(x) \stackrel{(2.35)}{=} N_{D_0} e^{-\frac{x^2}{\lambda^2}} \quad (2.40)$$

Dieses Gleichungssystem ist allerdings nicht geschlossen lösbar.

Oft bedient man sich daher geschlossenen integrierbarer Ersatzfunktionen, um das Gauß-Profil nachzubilden. Als Beispiele seien die Exponential- und die Sigmoid-Funktion

genannt [5]:

$$N_D(x) = N_{D_0} e^{-\frac{x^2}{\lambda^2}} \approx N_{D_0} A e^{-B \frac{x}{\lambda}} \quad (2.41)$$

$$\approx N_{D_0} \frac{C}{1 + D e^{E \frac{x}{\lambda}}} \quad (2.42)$$

Nachteilig sind hierbei die Parameter  $A$  bis  $E$ , die je nach zu untersuchendem Bereich angepaßt werden müssen.

Ein anderer, in dieser Arbeit verfolgter Weg, liegt in der numerischen Lösung mittels eines Device-Simulators. Hierfür stand das Programm MEDICI zur Verfügung, welches die Poisson-Gleichung (2.18) sowie die Kontinuitäts- und Transportgleichungen (2.4) zweidimensional löst.

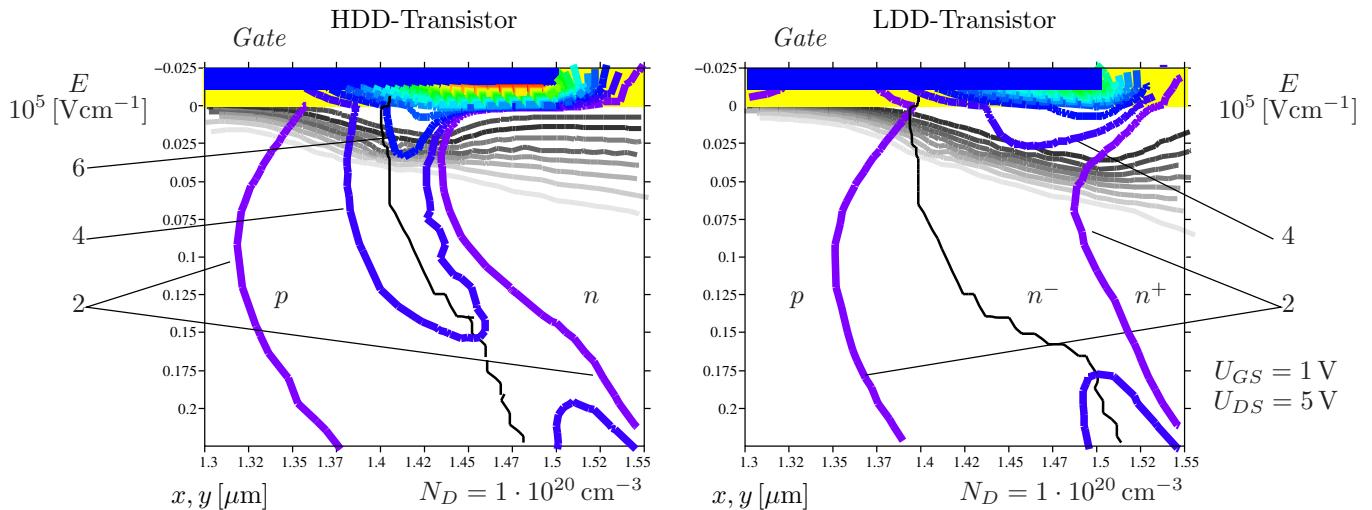

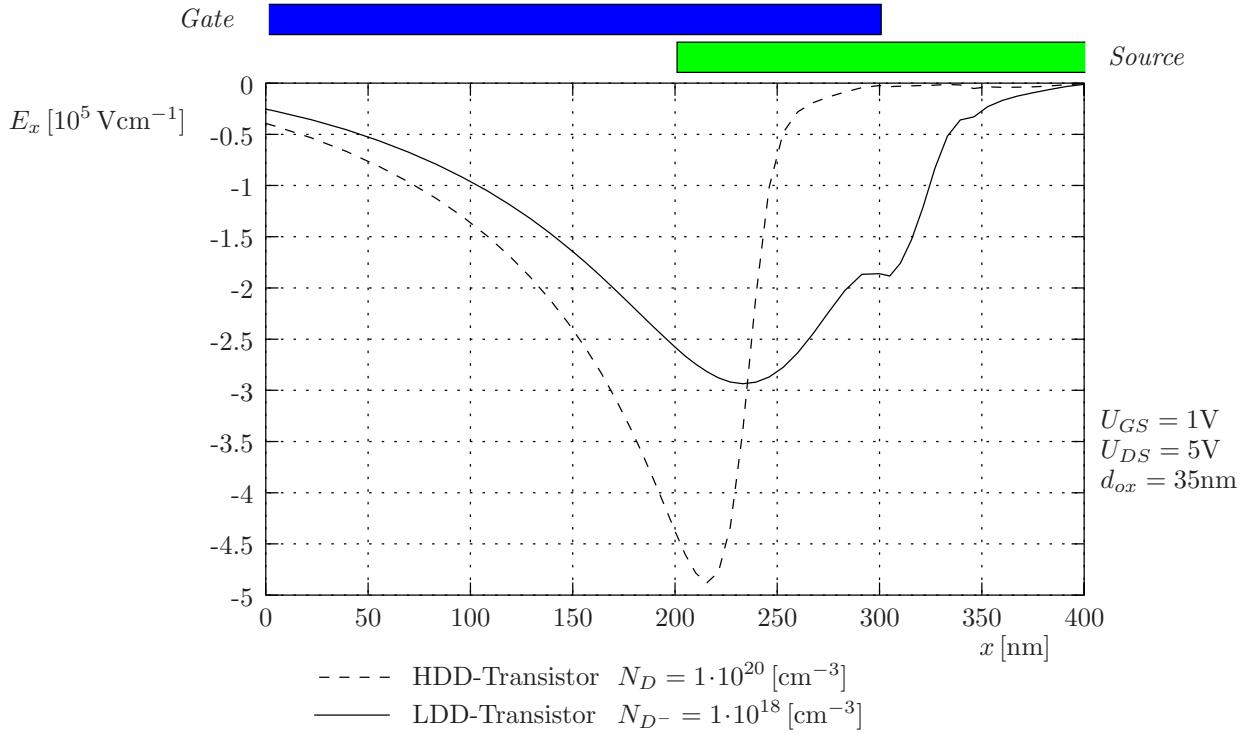

## 2.3 Elektrische Feldstärke

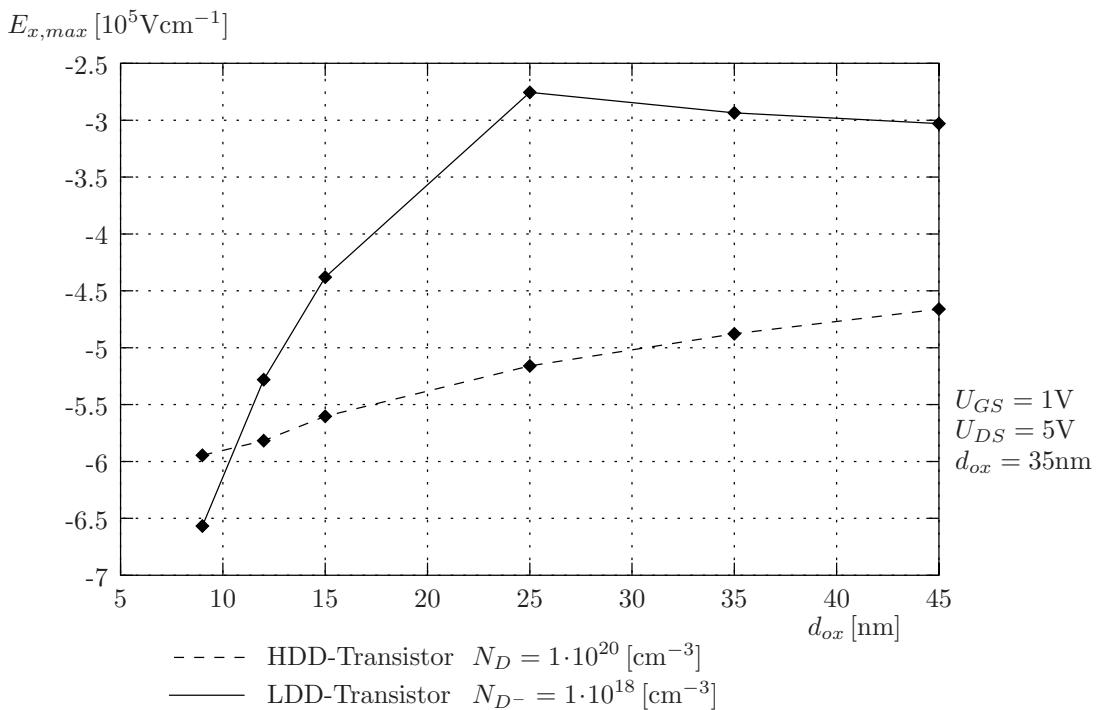

Abbildung 2.6 zeigt einen Kontur-Plot, der an der LDD-Drain auftretenden Feldstärke. Der Vergleich mit einem konventionellen Transistor ohne LDD zeigt bei gleicher Spannungsbelegung höhere Feldstärken. Der Strom löst sich im Unterdiffusionsgebiet des LDD-Transistors weiter von der Oberfläche ab; diese ist stärker verarmt.

Abbildung 2.6: Elektrische Feldstärke und Stromverlauf im Drain-Gebiet

Macht man einen lateralen Schnitt an der Grenze zwischen Halbleiter und Oxid und

trägt entlang dieses Schnittes die  $x$ -Komponente der Feldstärke auf, so erhält man die Verläufe aus Abbildung 2.7.

Abbildung 2.7: Laterale Komponente der Feldstärke an der Si–SiO<sub>2</sub>-Halbleiteroberfläche

Es zeigt sich, analog zu den Überlegungen am  $pn^-n^+$ -Übergang, ein kleinerer Feldstärke-Peak, der in das Überlappgebiet der Drain verschoben ist. Die Feldstärke fällt moderater ab.

Diese beiden Kurvenverläufe werden in zahlreichen Publikationen zur Begründung der LDD-Struktur herangezogen [19, 23, 16].

Simulationen ergaben jedoch, daß diese Kurvenverläufe nur für große Oxiddicken einer Verifikation standhalten. Verjüngt man hingegen das Oxid auf heutzutage übliche Dicken von etwa 9 nm, so zeigt sich ein erstaunliches Ergebnis: Die maximale laterale Feldstärke in der Halbleiteroberfläche übertrifft beim LDD-Transistor die des konventionellen Transistors.

Wie ist dies zu erklären?

Bisher wurde davon ausgegangen, daß das elektrische Feld lediglich auf der Diffusionsspannung der Übergänge sowie der Drain-Source-Spannung beruht. Senkrecht überla-

gert wird dieses Feld durch das Feld der Gate-Substrat-Spannung. Für die Transistormodellierung nimmt man überlicherweise an, daß dieses Feld rein vertikal ausgerichtet ist (*Gradual channel*-Näherung), was aber in den Randbereichen nicht zutrifft. Dort erlangt das Feld entsprechend der Gate-Source- bzw. der Gate-Drain-Spannung horizontale Komponenten. Diese sind wegen der nach außen verlagerten hochdotierten Gebiete beim LDD-Transistor ausgeprägter als bei einem konventionellen Transistor. Dieser Effekt der Feldüberlagerung wird für dünne Oxide immer dominanter, was eine ausgefeilte Dotierungsverteilung notwendig macht. Abbildung 2.8 zeigt die maximale vertikale Feldstärke in Abhängigkeit von der Oxiddicke.

Abbildung 2.8: Maximale laterale Feldstärkekomponente an der Halbleiteroberfläche in Abhängigkeit von der Oxiddicke

Folglich reicht eine eindimensionale Betrachtung an der Halbleiteroberfläche nicht aus, um LDD-Strukturen zu rechtfertigen. Adäquat sind hierfür zweidimensionale Feldverteilungen wie in Abbildung 2.6.

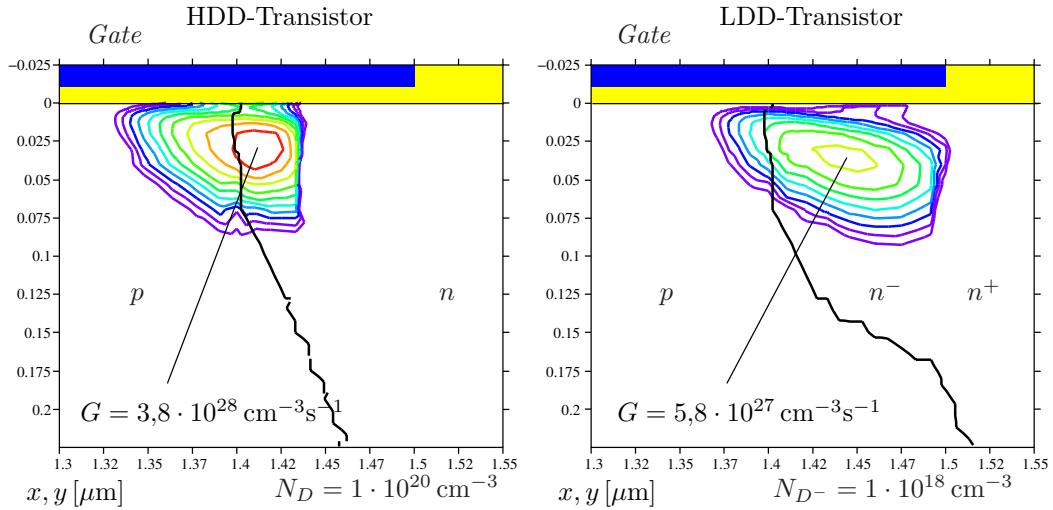

## 2.4 Stoßionisation

Einleitend wurde behauptet, die geringeren Feldstärken eines LDD-Transistors würden dessen Lebensdauer verlängern. Dies bedarf einer näheren Erläuterung.

Ist die lokale Feldstärke in einem Bauelement groß genug, so erlangt ein Ladungsträger innerhalb seiner mittleren freien Beschleunigungsstrecke eine kinetische Energie, die ausreicht, um beim Auftreffen auf ein Silizium- oder Dotieratom ein Elektron aus dem Gitter herauszuschlagen. Das herausgeschlagene Elektron hinterläßt ein Loch als Fehlstelle, so daß letztlich ein Ladungsträgerpaar entsteht. Man nennt diesen Vorgang *Stoßionisation*. Das so entstandene Elektron-Loch Paar kann wiederum neue Ladungsträger freisetzen, wenn bis zum Stoß ausreichend kinetische Energie gewonnen wird. Bei einer bestimmten kritischen Feldstärke setzt eine lawinenartige Ladungsträgermultiplikation ein. Man spricht daher vom Lawineneffekt (*avalanche effect*).

Durch das elektrische Feld werden die generierten Ladungsträger getrennt. Löcher wandern in das Substrat und können als Bulk-Strom nachgewiesen werden, während Elektronen in Bereiche höheren Potentials beschleunigt werden. Erlangen die Ladungsträger dabei hohe Energie, werden sie als „heiße Ladungsträger“ (*hot carriers*) bezeichnet.

Diese können beim Auftreffen auf das Oxid Gitterverbindungen aufbrechen und so Grenzflächenzustände generieren, welche, je nach Betriebszustand des Transistors, positiv oder negativ besetzt werden. Hochenergetische Ladungsträger können auch *im Oxid* Zustände generieren und besetzen.

Diese Effekte nennt man *Alterung* oder *Degradation*. Sie haben eine Verschiebung der Einsatzspannung zur Folge und können zur Zerstörung des Transistors führen.

Die Generationsrate durch Stoßionisation ist proportional zur Geschwindigkeit der Ladungsträger und deren Dichte. Sie wird durch das *Chynoweth-Gesetz* beschrieben [3]:

$$G = \alpha_n |\vec{v}_n| n + \alpha_p |\vec{v}_p| p = \alpha_n \frac{|\vec{j}_n|}{q} + \alpha_p \frac{|\vec{j}_p|}{q} \quad (2.43)$$

$\alpha_n$  und  $\alpha_p$  sind die Ionisierungsraten für Elektronen und Löcher; sie sind stark vom elektrischen Feld abhängig und gehorchen näherungsweise empirischen Funktionen.

$$\alpha_{n,p} = A_{n,p} e^{-\frac{B_{n,p}}{|\vec{E}|}} \quad (2.44)$$

$A_{n,p}, B_{n,p}$  : Konstanten

Hohe laterale Felder werden bei großen Drain-Source-Spannungen erreicht. Der Transistor ist dann „in Sättigung“, d. h. der Drain-Strom bleibt bei Variation der Spannung

annähernd konstant. Wie in Kapitel 3 näher erläutert wird, löst sich im drain-seitigen Kanalbereich der Strom von der Halbleiteroberfläche. Folglich findet man die größten Stoßionisationsraten ebenfalls in vertikaler Richtung versetzt vor. Abbildung 2.9 zeigt deren typische Verläufe.

Abbildung 2.9: Stoßionisation im Drain-Gebiet für einen Transistor in Sättigung ( $U_{GS} = 1 \text{ V}$ ,  $U_{DS} = 5 \text{ V}$ ), drei Konturlinien entsprechen einer Dekade in der Generationsrate

Der Vergleich zeigt eine um den Faktor 10 reduzierte Generationsrate beim Transistor mit LDD.

Des weiteren zeigt sich auch hier, daß die im vorigen Abschnitt monierte, auf die Halbleiteroberfläche reduzierte Betrachtung des LDD-Gebietes unzureichend ist. Schließlich kann die verminderte Alterung infolge geringerer Stoßionisation beim LDD-Transistor nur durch gleichzeitige Betrachtung von Strom- *und* Feldverlauf erklärt werden.

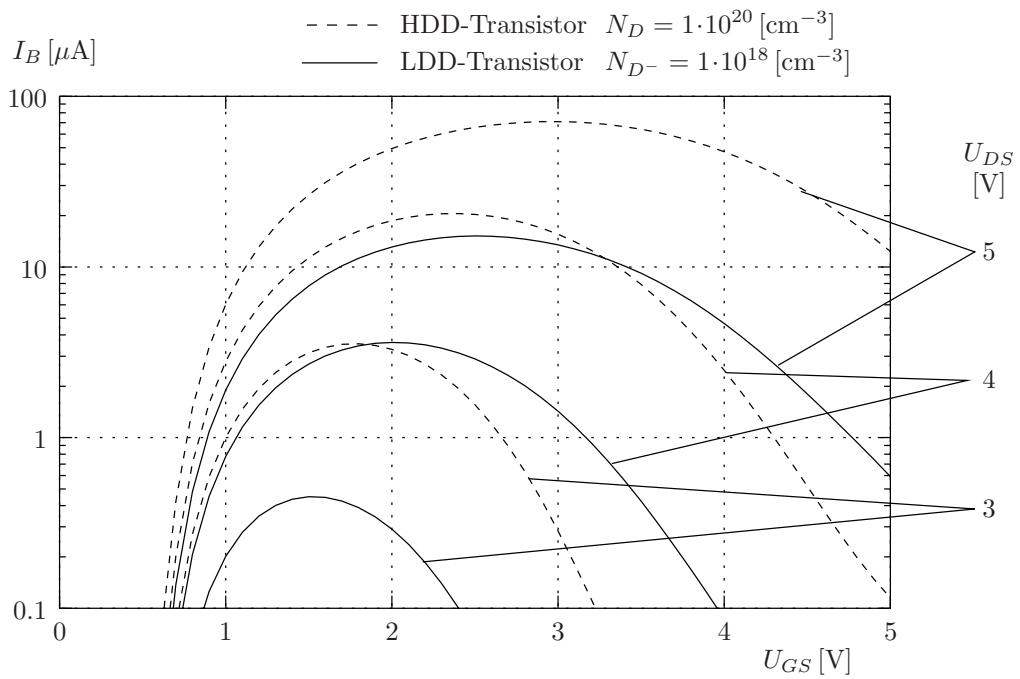

## 2.5 Substratstrom

Wie bereits erwähnt, korreliert die Stoßionisation mit dem Substratstrom und kann daher durch Messung quantifiziert werden. Abbildung 2.10 zeigt den simulierten Bulk-Strom in Abhängigkeit von der Gate-Source-Spannung.

Ist der Transistor ausgeschaltet, beruht der Substratstrom lediglich auf thermischer

Abbildung 2.10: Durch Stoßionisation im Drain-Gebiet verursachter Substratstrom

Generation und ist vernachlässigbar. Mit steigender Gate-Bulk-Spannung löst der anschwellende Drain-Strom vermehrt Stoßionisation aus; der Substratstrom steigt um mehrere Dekaden. Ab einer Gate-Bulk-Spannung, die typischerweise etwa der halben Drain-Source-Spannung entspricht, sinkt der Strom wieder. Dies ist auf die verminderte Potentialdifferenz zwischen Gate und Drain zurückzuführen.

# Kapitel 3

## Modellierung des MOS-Transistors

In diesem Kapitel werden für die spätere Verwendung die Grundgleichungen eines *n*-Kanal MOSFETs hergeleitet.

Näherungsweise nimmt man hierfür an, daß das zwischen Gate und Kanal herrschende Feld wesentlich größer ist als das Feld zwischen Source und Drain. Dadurch wird ein eindimensionaler Ansatz ermöglicht. In der Realität treten deutliche Abweichungen von dieser Näherung an den Rändern des Gates und in der Umgebung der *pn*-Übergänge auf. Dies hat zur Folge, daß dieser Grundansatz vornehmlich sogenannten *Langkanaltransistoren* genüge leistet.

Ist die Gate-Bulk-Spannung vernachlässigbar gering ( $U_{GB} \approx 0$ ), der Transistor also ausgeschaltet, so wird der Drain-Strom durch die exponentiell verlaufende Diodenkennlinie der gesperrten *pn*-Übergänge beschrieben. Es ist kein nennenswerter Stromfluß möglich.

Mit zunehmender Gate-Bulk-Spannung steigt das Oberflächenpotential  $\phi_s$ , wodurch die Löcher im Substrat von der Halbleiteroberfläche verdrängt werden. Die zurückbleibenden Akzeptorrümpfe  $N_A^-$  bilden eine Raumladungszone, deren Ausdehnung entsprechend der Gleichung (2.29) beschrieben werden kann.

$$y_{depl} = \sqrt{2 \frac{\varepsilon_0 \varepsilon_{si}}{q} \frac{1}{N_A} \phi_s} \quad (3.1)$$

Das Potential an der Halbleiteroberfläche  $\phi_s = \phi(y=0)$  entspricht dabei der über der Raumladungszone abfallenden Spannung, wenn man als Bezugspunkt das Potential im neutralen Substratgebiet wählt. Berücksichtigt man ferner die an den Kontakten

abfallende Flachbandspannung  $U_{fb}$ , so läßt sich der Spannungsabfall über das Oxid mit der Terminalspannung  $U_{GB}$  verknüpfen.

$$\phi_{ox} = U_{GB} - U_{fb} - \phi_s \quad (3.2)$$

Bei weiterer Erhöhung der Gate-Bulk-Spannung erreicht das Oberflächenpotential einen Wert, bei dem mindestens einer der  $pn$ -Übergänge in Durchlaßrichtung geht. Für symmetrische Dotierungsprofile und  $U_{DS} > 0$  ist dies der source-seitige Übergang. Elektronen werden in das Substrat injiziert und bilden infolge der elektrostatischen Anziehung des Gates an der Halbleiteroberfläche eine dünne Schicht aus. Sie lösen dort also Löcher in ihrer Rolle als Majoritätsladungsträger ab. Daher nennt man diesen Zustand *Inversion* und bezeichnet die Elektronenschicht als *Inversionsladung*.

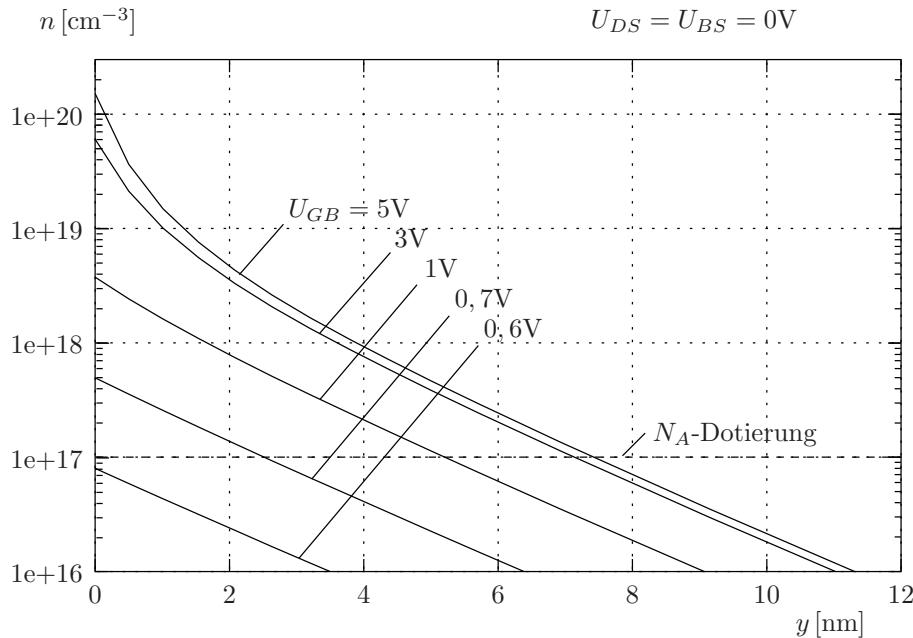

Diese ist jedoch derart dünn ( $\approx 5 \text{ nm}$ ), daß man den Spannungsabfall darüber vernachlässigen kann (Abbildung 3.1).

Abbildung 3.1: Die lokale Verteilung der Inversionsschichtladung in der Mitte des Kanals für verschiedene Gate-Substrat-Spannungen

Diese häufig in der Bauelementemodellierung angewandte Vereinfachung wird *Charge sheet*-Näherung genannt. Sie bewirkt, daß die gesamte Potentialdifferenz  $\phi_s$  über der Verarmungszone abfällt. Die Gateladung pro Fläche  $Q'_G$  läßt sich wie bei einem Plattenkondensator berechnen.

$$Q'_G = C'_{ox} \phi_{ox} = C'_{ox} (U_{GB} - U_{fb} - \phi_s) \quad (3.3)$$

$C'_{ox} = \frac{\varepsilon_0 \varepsilon_{si}}{d_{ox}}$  ist die Kapazität des Oxids pro Fläche und  $d_{ox}$  die Dicke der Oxidschicht. Der Gateladung muß eine größengleiche Ladung entgegengesetzten Vorzeichens im Halbleiter gegenüberstehen. Diese besteht aus zwei Komponenten — der Ladung der Inversionsschicht sowie der der Raumladungszone.

$$Q'_G = -(Q'_I + Q'_B) \quad (3.4)$$

Zusätzliche Ladungen auf dem Gate werden überwiegend durch zusätzliche Ladungen in der Inversionsschicht kompensiert; die Flächenladung  $Q'_B$  der Raumladungszone bleibt nahezu unverändert und wird durch Multiplikation der Ionenladungsdichte mit der Tiefe der Raumladungszone (3.1) bestimmt (*Depletion*-Näherung).

$$Q'_B = -q N_A \cdot \sqrt{2 \frac{\varepsilon_0 \varepsilon_{si}}{q} \frac{1}{N_A} \cdot \phi_s} = -\sqrt{2 \varepsilon_0 \varepsilon_{si} q N_A \cdot \phi_s} \quad (3.5)$$

Somit läßt sich die für die Charakteristik eines Transistors bedeutsame Inversionsschichtladung bestimmen (3.4 und 3.5).

$$Q'_I = -Q'_G - Q'_B = -C'_{ox} (U_{GB} - U_{fb} - \phi_s) + \sqrt{2 \varepsilon_0 \varepsilon_{si} q N_A \cdot \phi_s} \quad (3.6)$$

Das Oberflächenpotential zu Beginn der Inversion läßt sich aus der Bedingung ableiten, daß die Elektronenkonzentration an der Halbleiteroberfläche (2.11)

$$n(y=0) = n_i e^{-\frac{E_F - E_i(y=0)}{kT}} \quad (3.7)$$

gerade die der Löcher im Substrat (2.11)

$$p(y \rightarrow \infty) = n_i e^{-\frac{E_i(y \rightarrow \infty) - E_F}{kT}} \quad (3.8)$$

erreicht:

$$\phi_{s,inv} = \phi_{inv}(y=0) = \frac{1}{q} (E_i(y=0) - E_i(y \rightarrow \infty)) = \frac{1}{q} \cdot 2 E_F = 2 \phi_F \quad (3.9)$$

$\phi_F$  wird Fermispannung genannt. Nimmt man hingegen die Löcherkonzentration an der Oberfläche als Vergleichswert, so erhält man als Potential  $\phi_{s,inv} = \phi_F$ . Die Elektronenkonzentration erreicht dann gerade die Intrinsic-Dichte.

Da für ein Oberflächenpotential zwischen  $\phi_F$  und  $2 \phi_F$  der Kanal nur gering ausgeprägt ist, bezeichnet man diesen Bereich als *schwache Inversion*; oberhalb von  $2 \phi_F$  spricht man von *starker Inversion*.

Den Betriebsmodus, bei dem im Kanal schwache Inversion vorliegt, nennt man *Unterschwellstrombereich*. Da in diesem Arbeitsbereich der Widerstand des Kanals dominiert,

in dieser Arbeit das Hauptaugenmerk aber auf den äußeren Widerständen liegt, soll er nicht weiter untersucht werden.

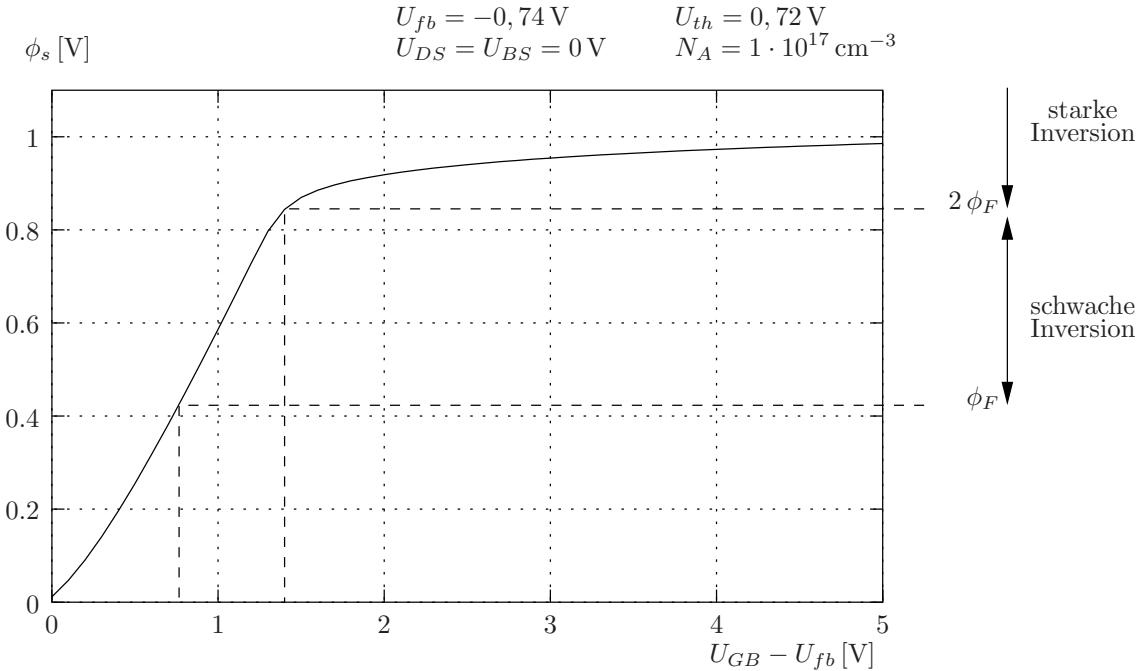

Wegen des exponentiellen Zusammenhangs der Elektronendichte und dem Bandabstand (2.11) bleibt das Oberflächenpotential jedoch auch für höhere Gate-Bulk-Spannungen nahezu konstant ( $\phi_s \approx \phi_{s,inv}$ ). Abbildung 3.2 stellt diese Zusammenhänge für einen vertikalen Schnitt im Kanal dar.

Abbildung 3.2: Das Oberflächenpotential im Kanalbereich in Abhängigkeit von der Gate-Bulk-Spannung

Legt man ferner eine Spannung zwischen Source und Bulk — diese wird stets positiv, also in Sperrrichtung der  $pn$ -Übergänge gewählt —, so erhöht sich das zur (starken) Inversion benötigte Potential entsprechend

$$\phi_s = 2\phi_F + U_{SB} \quad (3.10)$$

Gleichung (3.6) lässt sich somit folgendermaßen schreiben:

$$\begin{aligned}

Q'_I &= -C'_{ox} (U_{GB} - U_{fb} - (2\phi_F + U_{SB})) + \sqrt{2\varepsilon_0\varepsilon_{si}qN_A \cdot (2\phi_F + U_{SB})} \\

&= -C'_{ox} (U_{GB} - U_{fb} - (2\phi_F + U_{SB})) - \gamma \cdot \sqrt{2\phi_F + U_{SB}} \\

&= -C'_{ox} (U_{GS} - U_{th}) \quad \text{für } U_{GS} \geq U_{th} \\

&\approx 0 \quad \text{für } U_{GS} \ll U_{th}

\end{aligned} \quad (3.11)$$

Die Spannung  $U_{th}$  nennt man Einsatzspannung (*threshold voltage*) des MOS-Transistors. Sie ist definiert als die aus dem Bereich starker Inversion extrapolierte Gate-Source-Spannung, für die die Inversionsschichtladung gleich Null ist.

$$\begin{aligned} U_{th} = U_{GS}(Q'_I = 0) &= U_{fb} + 2\phi_F + \frac{\sqrt{2\varepsilon_0\varepsilon_{si}qN_A \cdot (2\phi_F + U_{SB})}}{C'_{ox}} \\ &= U_{fb} + 2\phi_F + \gamma \cdot \sqrt{2\phi_F + U_{SB}} \end{aligned} \quad (3.12)$$

Hierbei wurde eine Substitution vorgenommen:

$$\gamma = \frac{1}{C'_{ox}} \sqrt{2\varepsilon_0\varepsilon_{si}qN_A} \quad (3.13)$$

Diesen Faktor  $\gamma$  bezeichnet man als *Substratsteuerfaktor*, da er den Einfluß des Substratpotentials auf die Einsatzspannung beschreibt. Dieser Einfluß beruht auf der unterschiedlichen Aufteilung der Ladungen in der Inversionsschicht und in der Raumladungszone. Wird zum Beispiel die Spannung zwischen Source und Bulk erhöht, so nimmt die Weite und damit die Ladung der Verarmungszone zu, und aus der Ladungserhaltung folgt eine reduzierte Inversionsladung. Demzufolge steigt die Einsatzspannung und führt zu einem geringeren Stromfluß zwischen Drain und Source.

Letzteres ist ersichtlich aus der nun folgenden Herleitung des Drain-Stroms.

### 3.1 Widerstandsbereich

Die Inversionsschicht bildet zwischen Source und Drain einen leitenden Kanal und ermöglicht so einen Stromfluß. Voraussetzung hierfür sind allerdings unterschiedliche Potentiale an Source und Drain, wodurch auch das Oberflächenpotential ortsabhängig wird (3.10):

$$\phi_s(x) = 2\phi_F + U_{SB} + \Delta\phi(x) \quad (3.14)$$

$\Delta\phi(x)$  ist die Potentialänderung längs des Kanals; an der Source-Seite habe sie den Wert Null. Diese Variation hat jedoch auf die Tiefe der Verarmungszone kaum Einfluß. Man kann daher in guter Näherung die Wurzel aus Gleichung (3.11) linearisieren:

$$\begin{aligned} Q'_I(x) &= -C'_{ox} \left[ U_{GB} - U_{fb} - (2\phi_F + U_{SB} + \Delta\phi(x)) \right. \\ &\quad \left. - \gamma \cdot \sqrt{2\phi_F + U_{SB} + \Delta\phi(x)} \right] \end{aligned}$$

$$\begin{aligned}

&\approx -C'_{ox} \left[ U_{GB} - U_{fb} - (2\phi_F + U_{SB} + \Delta\phi(x)) \right. \\

&\quad \left. - \gamma \cdot (\sqrt{2\phi_F + U_{SB}} + \frac{1}{2\sqrt{2\phi_F + U_{SB}}} \cdot \Delta\phi(x)) \right] \\

&= -C'_{ox} \left[ U_{GS} - U_{th} - \Delta\phi(x) - \gamma \cdot \frac{1}{2\sqrt{2\phi_F + U_{SB}}} \cdot \Delta\phi(x) \right] \\

&= -C'_{ox} \left[ U_{GS} - U_{th} - (1 + \delta) \cdot \Delta\phi(x) \right]

\end{aligned} \tag{3.15}$$

Der Faktor  $\delta = \frac{\gamma}{2\sqrt{2\phi_F + U_{SB}}}$  erfaßt hierbei die Ortsabhängigkeit der Raumladungszone. Oberhalb der Einsatzspannung ist die Diffusionsstrom vernachlässigbar. Der Drain-Strom läßt sich daher mit dem Driftstrom (2.2), verursacht durch die Potentialänderung längs des Kanals, beschreiben.

$$\begin{aligned}

I_D(x) &= -I_{drift} = w \mu_n Q'_I E_x = -w \mu_n Q'_I \frac{d\Delta\phi}{dx} \\

&\stackrel{(3.15)}{=} w \mu_n C'_{ox} [U_{GS} - U_{th} - (1 + \delta) \cdot \Delta\phi(x)] \frac{d\Delta\phi}{dx}

\end{aligned} \tag{3.16}$$

Die Potentialdifferenz zwischen Ende ( $x=l$ ) und Anfang ( $x=0$ ) des Kanals entspricht annähernd der zwischen Drain und Source angelegten Spannung  $U_{DS}$ . Durch Trennen der Variablen und Integration über die Kanallänge  $l$  läßt sich die vorige Gleichung auswerten:

$$\int_{x=0}^{x=l} I_D dx = \int_{\Delta\phi(x=0)=0}^{\Delta\phi(x=l)=U_{DS}} w \mu_n C'_{ox} [U_{GS} - U_{th} - (1 + \delta) \cdot \Delta\phi(x)] d\Delta\phi \tag{3.17}$$

$$I_D = \frac{w}{l} \mu_n C'_{ox} \left[ (U_{GS} - U_{th}) U_{DS} - \frac{1}{2}(1 + \delta) U_{DS}^2 \right] \tag{3.18}$$

Es ergibt sich ein parabelförmiger Verlauf von  $I_D$  mit  $U_{DS}$ .

Physikalisch sinnvoll ist jedoch nur der Teil, bei dem der Drain-Strom mit der Drain-Source-Spannung wächst. Man bezeichnet diesen Bereich als *Widerstands-* oder *Triodenbereich*. Das Strommaximum ergibt sich für

$$U_{DS} = U_{DS_{sat}} = \frac{1}{1 + \delta} \cdot (U_{GS} - U_{th}) \tag{3.19}$$

und hat einen Wert von

$$I_D = I_{D(u_{DS}=(u_{GS}-u_{th})/(1+\delta))} = \frac{w}{2l} \mu_n C'_{ox} (1 + \delta) (U_{GS} - U_{th})^2 \tag{3.20}$$

$U_{DS_{sat}}$  wird *Sättigungsspannung* genannt.

## 3.2 Sättigungsbereich

Für Drain-Source-Spannungen oberhalb von  $U_{DS_{sat}}$  spricht man vom *Sättigungsbereich* des Transistors. Hier verliert der beschriebene eindimensionale Ansatz seine Gültigkeit. Bei der Herleitung der Inversionsladung wurde nämlich nur das vom Gate-Potential herrührende vertikale Feld betrachtet. Bei größeren Drain-Source-Spannungen gewinnt aber auch das laterale Feld Einfluß auf die Kanalladung.

Nach Gleichung (3.15) wird die Inversionsschichtladung bei einem bestimmten Wert des Kanalpotentials  $\Delta\phi$  Null und wechselt sogar das Vorzeichen bei weiterem Anstieg von  $\Delta\phi$ . Dies bedeutet, daß die Ladungsdichte immer geringer wird, je weiter man sich der Drain nähert. Aus der Kontinuität des Stromes folgt daher ein Anstieg des elektrischen Feldes.

Dies ist der Grund dafür, daß eine LDD-Dotierung für  $U_{DS} > 0$  eigentlich nur drainseitig vornötigen ist. Anschaulich wird dies auch, wenn man sich vor Augen führt, daß die Elektronen beim Durchlaufen der Drain-Source-Spannung immer schneller werden. Beim Eintritt in die Drain erreichen sie ihre maximale Geschwindigkeit und lösen dort vermehrt Stoßionisation aus. Um die Produktion des Transistors zu vereinfachen, wählt man jedoch den auf Seite 6 illustrierten symmetrischen Aufbau.

Will man den Transistor auch im Sättigungsbereich beschreiben, wären komplizierte zweidimensionale Berechnungen erforderlich, die beide Feldkomponenten berücksichtigen.

Man umgeht dies, indem man die Integration der Gleichung (3.17) nur über den Teil des Kanals ausführt, für den die eindimensionale Näherung noch zulässig ist. In den oberen Integrationsgrenzen ersetzt man also die Kanallänge  $l$  durch einen reduzierten Wert  $l' < l$ . Um einen ausgezeichneten Wert für  $l'$  zu erhalten, extrapoliert man in Gleichung (3.15) die Ladungsdichte auf Null; es ergibt sich:

$$\Delta\phi(x = l') = \frac{U_{GS} - U_{th}}{1 + \delta} \quad (3.21)$$

An diesem fiktiven Ort  $l'$  im Kanal verschwindet somit die Inversionsschicht, der Kanal wird eingeschnürt; daher seine englische Bezeichnung *pinch-off point*.

Mit diesen Integrationsgrenzen ergibt Gleichung (3.18) für den Drain-Strom:

$$I_D = \frac{w}{2l'} \mu_n C'_{ox} \frac{(U_{GS} - U_{th})^2}{1 + \delta} \quad (3.22)$$

Dies ist ein um den Faktor  $l/l'$  größerer Strom als der in Gleichung (3.20) berechnete Maximalstrom des Widerstandsbereichs.

Da der *pinch-off point* mit zunehmender Drain-Source-Spannung von der Drain wegwandert, erhöht sich also auch der Drain-Strom entsprechend. Für Langkanal-Transistoren fällt diese Kanalverkürzung jedoch nicht ins Gewicht ( $l' \approx l$ ), und der Drain-Strom kann als konstant angenommen werden.

Zusammengefaßt lauten die Stromgleichungen des  $n$ -Kanal MOSFETs in den verschiedenen Betriebszuständen:

- Unterschwellstrombereich ( $U_{GS} \leq U_{th}$ )

$$I_D \approx 0 \quad (3.23)$$

- Widerstandsbereich ( $U_{GS} > U_{th}, \quad 0 \leq (1 + \delta) \cdot U_{DS} < U_{GS} - U_{th}$ )

$$I_D = \frac{w}{l} \mu_n C'_{ox} \left[ (U_{GS} - U_{th}) U_{DS} - \frac{1}{2} (1 + \delta) U_{DS}^2 \right] \quad (3.24)$$

- Sättigungsbereich ( $U_{GS} > U_{th}, \quad U_{GS} - U_{th} \leq (1 + \delta) \cdot U_{DS}$ )

$$I_D = \frac{w}{2l'} \mu_n C'_{ox} \frac{1}{1 + \delta} (U_{GS} - U_{th})^2 \quad (3.25)$$

$$\text{mit } \delta = \frac{\gamma}{2\sqrt{2\phi_F + U_{SB}}} \quad (3.26)$$

$$\gamma = \frac{1}{C'_{ox}} \sqrt{2\epsilon_0 \epsilon_{si} q N_A} \quad (3.27)$$

$$U_{th} = U_{fb} + 2\phi_F + \gamma \cdot \sqrt{2\phi_F + U_{SB}} \quad (3.28)$$

$$\phi_i = \frac{kT}{q} \ln \frac{N_A}{n_i} \quad (3.29)$$

$$C'_{ox} = \frac{\epsilon_0 \epsilon_{si}}{d_{ox}} \quad (3.30)$$

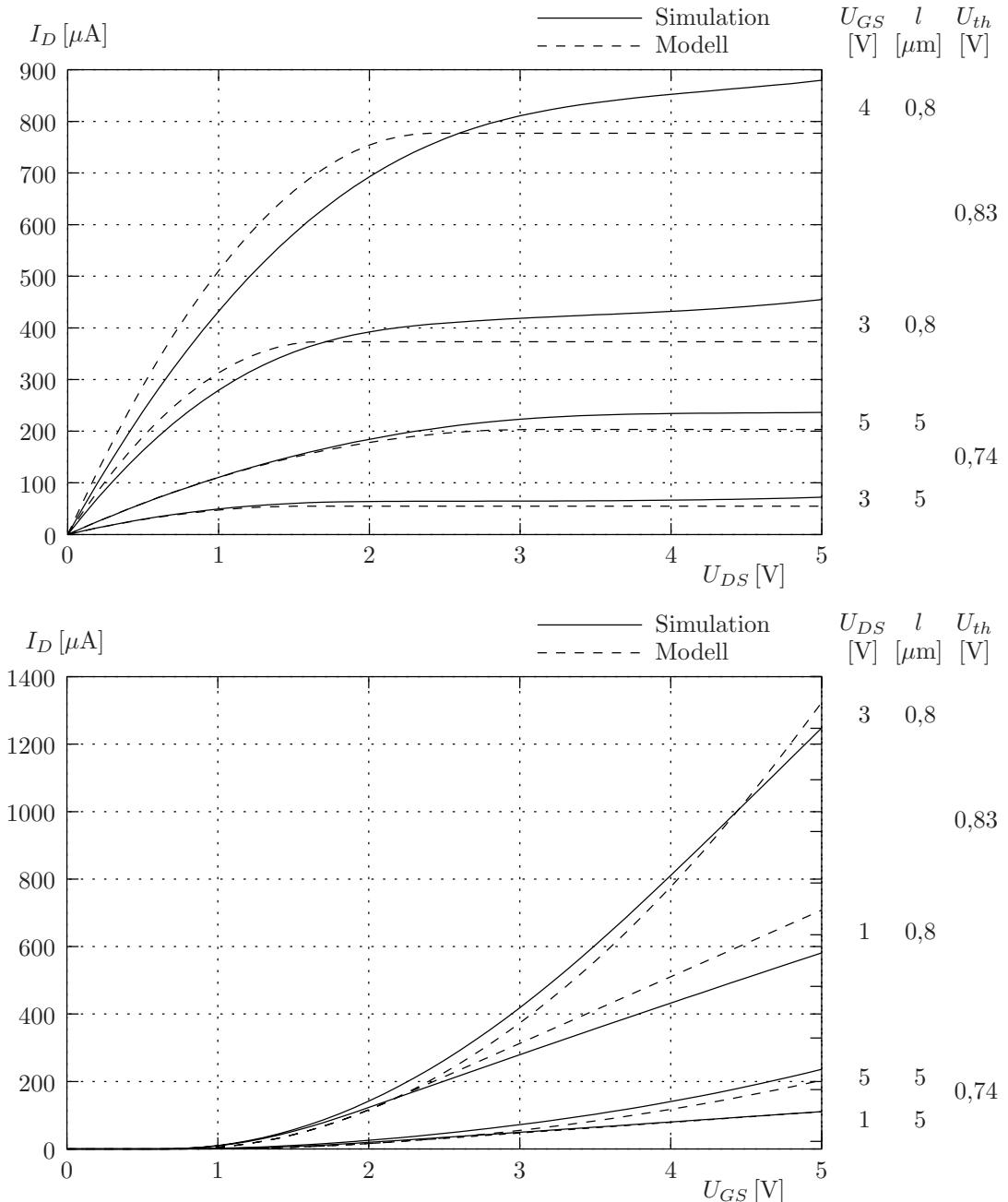

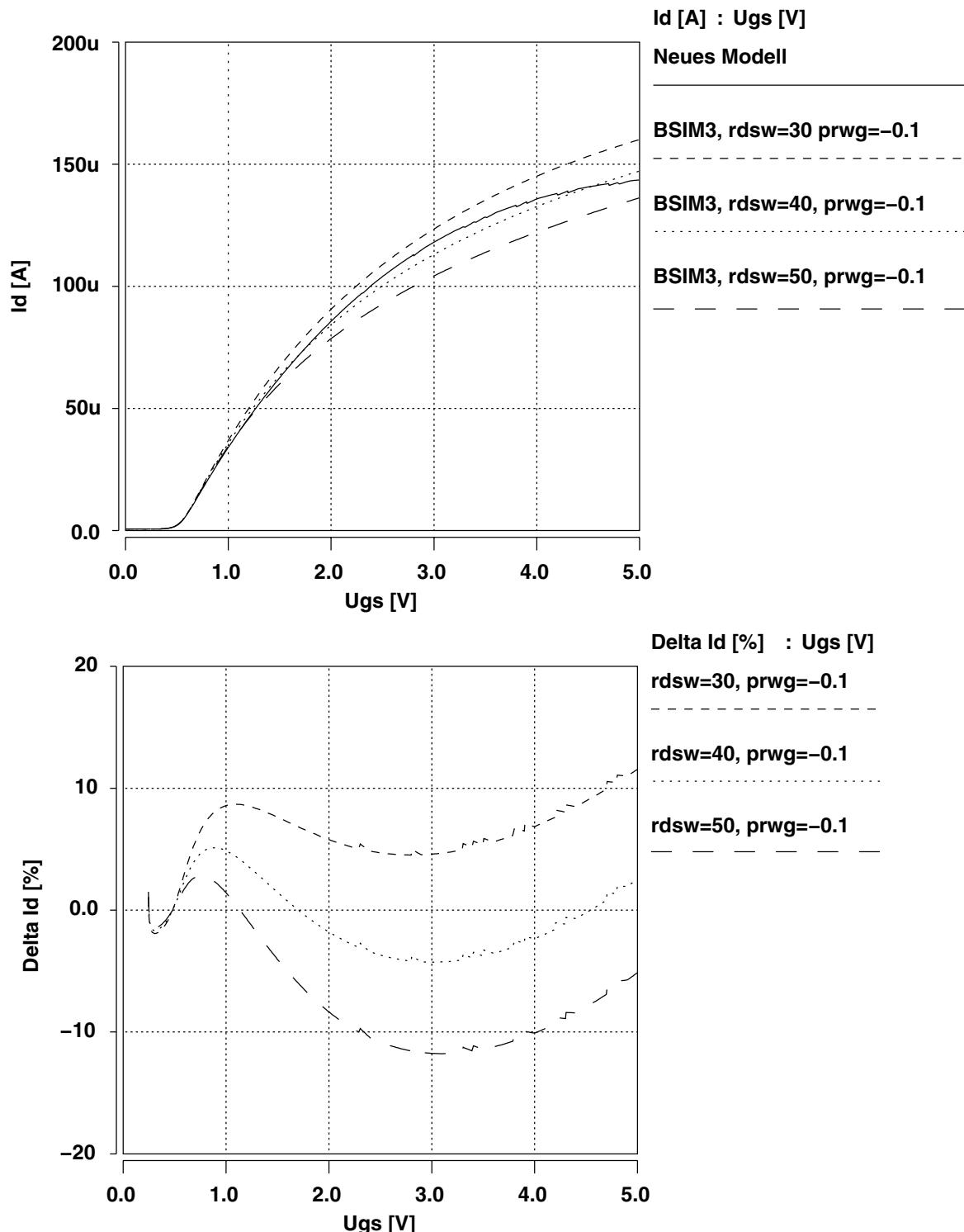

Abbildung 3.3 zeigt einen Vergleich zwischen diesen Modellgleichungen und MEDICI-Simulationen, sowohl für die *Eingangskennlinien* ( $I_D$  über  $U_{GS}$ ), als auch für die *Ausgang-/Transferkennlinien* ( $I_D$  über  $U_{DS}$ ).

Abbildung 3.3: Vergleich zwischen den Standard-Modellgleichungen und MEDICI-Simulationen für einen langen ( $l = 5 \mu\text{m}$ ) und einen kurzen ( $l = 0,8 \mu\text{m}$ ) Transistor

Die Charakteristik des Langkanälers ( $l = 5 \mu\text{m}$ ) wird durch die obigen einfachen Gleichungen recht gut beschrieben, während beim Kurzkanäler ( $l = 0,8 \mu\text{m}$ ) deutliche Abweichungen erkennbar sind.

Daher sind industrielle und wissenschaftliche Transistormodelle ungleich komplizierter und benötigen eine oft unüberschaubare Anzahl an Paßfaktoren.

# Kapitel 4

## Neues Widerstandsmodell

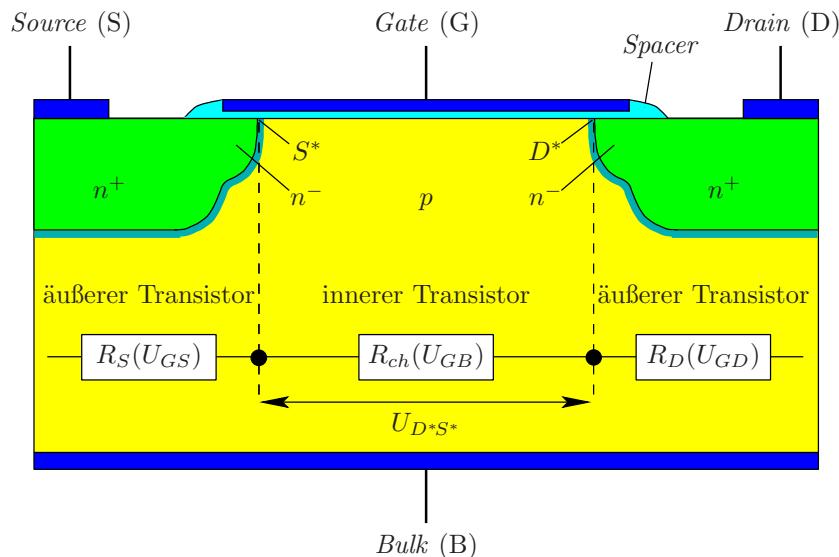

Für die Herleitung der Transistorgleichungen im vorigen Kapitel wurde angenommen, daß die von außen angelegte Spannung auch tatsächlich am inneren Transistor anliegt. Dieser erstreckt sich, wie Abbildung 4.1 zeigt, vom source-seitigen zum drain-seitigen *pn*-Übergang.

Abbildung 4.1: Aufteilung des LDD-MOS-Transistors in einen internen und einen externen Transistor

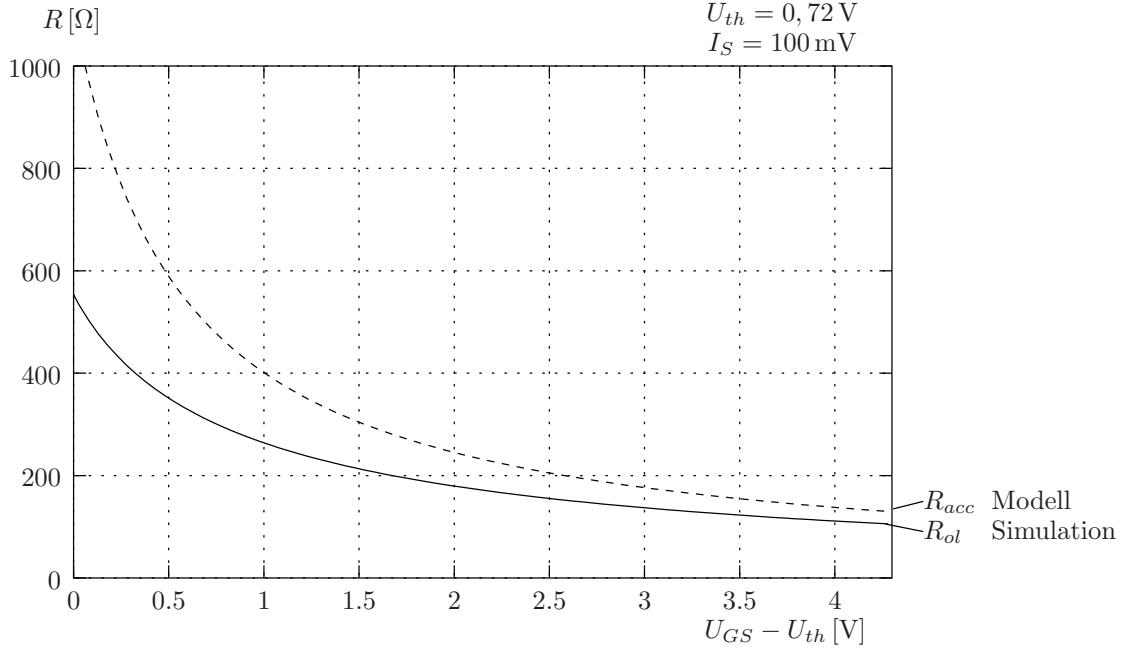

Somit werden Kontaktwiderstände, die Widerstände jenseits der Gate-Kante sowie der Überlappgebiete vernachlässigt. In der Tat sind aber gerade die zuletzt aufgeführten Widerstände, insbesondere bei LDD-Strukturen, nicht vernachlässigbar!

Das Grundmodell der Transistorgleichungen gilt also strenggenommen nur, wenn man, der Bezeichnung in Abbildung 4.1 entsprechend,  $U_{DS}$  durch  $U_{D^*S^*}$  und  $U_{SB}$  durch  $U_{S^*B}$  ersetzt. Außerdem sind die oben aufgeführten Widerstände des äußeren Transistors nicht konstant; vor allem der Widerstand im Überlappgebiet ist stark spannungsabhängig. Dies wird in den gängigen industriellen Modellen (BSIM3 v3, MOS C5, ...) jedoch nicht oder nur mangelhaft berücksichtigt.

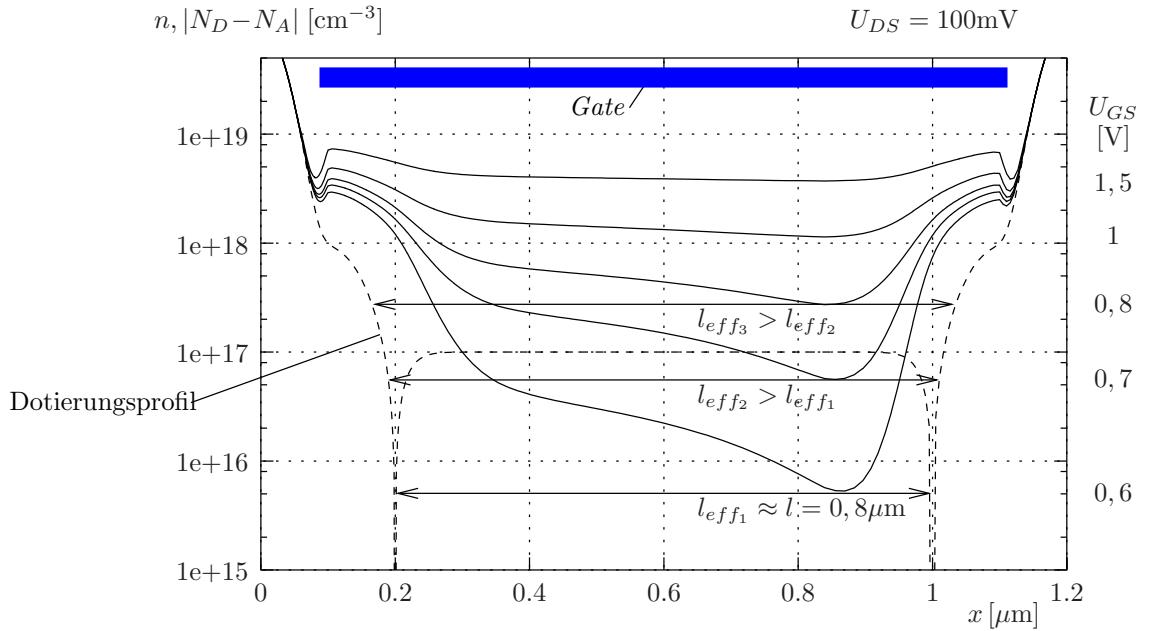

## 4.1 Effektive Kanallänge

Statt dessen behilft man sich mit konstanten parasitären Widerständen und verwendet an Stelle der geometrischen eine größere, effektive Kanallänge. Die Motivation hierfür ist nachstehender Abbildung 4.2 zu entnehmen, in der die Elektronenkonzentration sowie das Dotierungsprofil entlang der Halbleiteroberfläche aufgetragen sind. Der Transistor befindet sich im Widerstandsbereich. Man kann hieraus auch entnehmen, daß aufgrund der höheren Geschwindigkeit der Elektronen in Richtung zur Drain deren Konzentration abnimmt.

Eine Anhebung des Gatepotentials führt nicht nur zu einer Inversion des Kanalbereichs, sondern auch zu einer Akkumulation von Elektronen im Überlappgebiet. Dadurch verengert sich der Widerstand der Überlappgebiete, und der Kanal dehnt sich über seine geometrische Länge  $l$  hinweg aus. Diese Ausdehnung erfolgt für den Widerstandsbereich sowohl source- als auch drain-seitig.

Man kann die Ladung entlang der Halbleiteroberfläche des Unterdiffusionsgebietes grob in zwei Bereiche aufteilen: im einen dominieren die gate-induzierten Ladungsträger, im anderen werden sie durch die Dotierung bestimmt.

Eine Abschätzung der effektiven Kanallänge  $l_{eff}$  läßt sich treffen, indem man die minimale Elektronendichte als Referenz wählt und für diese Konzentration den Abstand zwischen Source- und Drain-Dotierung extrahiert. In anderen Worten: *Der Kanal endet dort, wo die gate-induzierte Ladung die gleiche Dichte hat wie diejenige, die durch die Dotierung erzeugt wird.* Daraus wird ersichtlich, daß die effektive Kanallänge  $l_{eff}$  von LDD-Transistoren, speziell im Bereich hoher Gate-Spannungen, stark von der geometrischen abweicht. Für konventionelle HDD-Transistoren (*highly doped drain*) ergibt sich hingegen eine vernachlässigbare Abweichung, da das Dotierungsprofil mit wesentlich steilerer Flanke abfällt.

Abbildung 4.2: Laterale Elektronenverteilung und Dotierungsprofil entlang der Halbleiteroberfläche

Pfeile symbolisieren die mit steigender Gate-Spannung anwachsende effektive Kanallänge

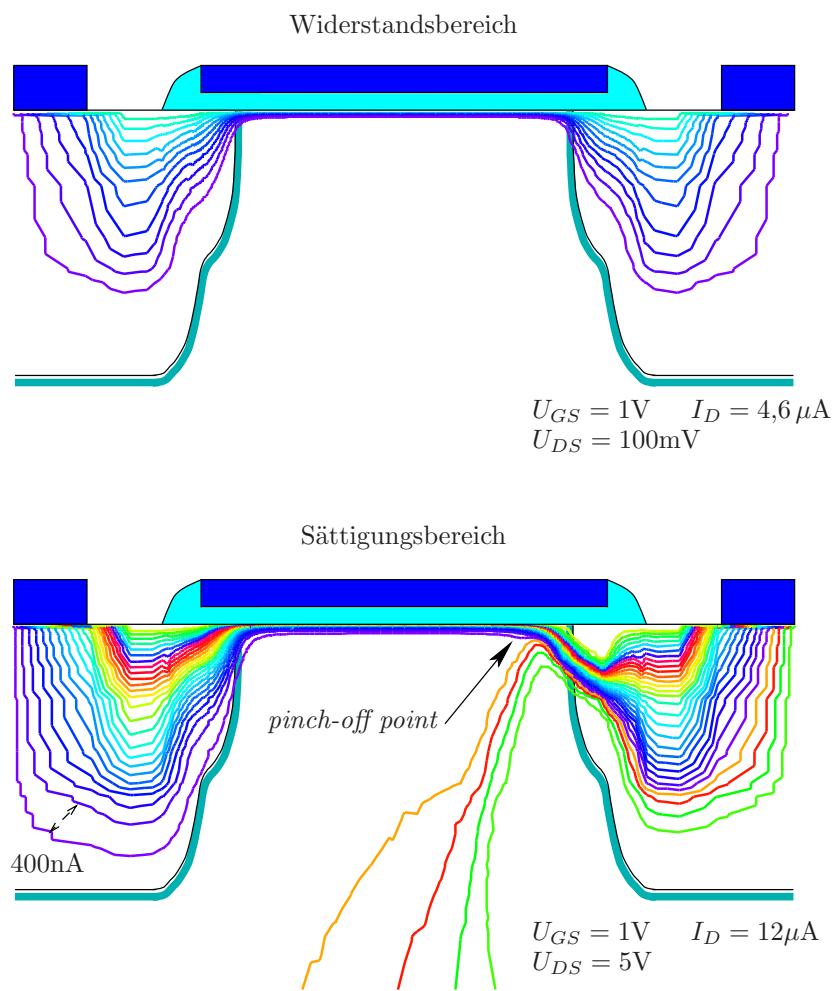

Im Sättigungsbereich ( $U_{GS} - U_{th} < U_{DS}$ ) wächst der Kanal nur auf der Source-Seite ins Überlappgebiet, da das rechte Ende des Kanals durch dessen Abschnürung am *pinch-off point* bestimmt ist, an dem sich der Strom von der Oberfläche löst. Abbildung 4.3 zeigt den Verlauf der Strompfade für beide Betriebsmoden.

Wegen der enormen Komplexität im Sättigungsbereich, beschränkt man sich bei der Modellierung vornehmlich auf den symmetrisch beschreibbaren Widerstandsbereich.

Abbildung 4.3: Symmetrischer Verlauf des Stroms im Widerstandsbereich und drain-seitige Stromablösung von der Oberfläche im Sättigungsbereich

### 4.1.1 Bestimmung der effektiven Kanallänge

Die Strom-Spannungs-Abhängigkeit wurde für den inneren Transistor im vorhergehenden Kapitel hergeleitet (3.24). Mit den modifizierten Indizes lautet sie:

$$I_D \simeq \frac{w}{l} \mu_n C'_{ox} \left[ (U_{GS} - U_{th}) U_{D^*S^*} - \frac{1}{2}(1 + \delta) U_{D^*S^*}^2 \right] \quad (4.1)$$

Hieraus lässt sich der Widerstand des Kanals (englisch *channel*) ableiten:

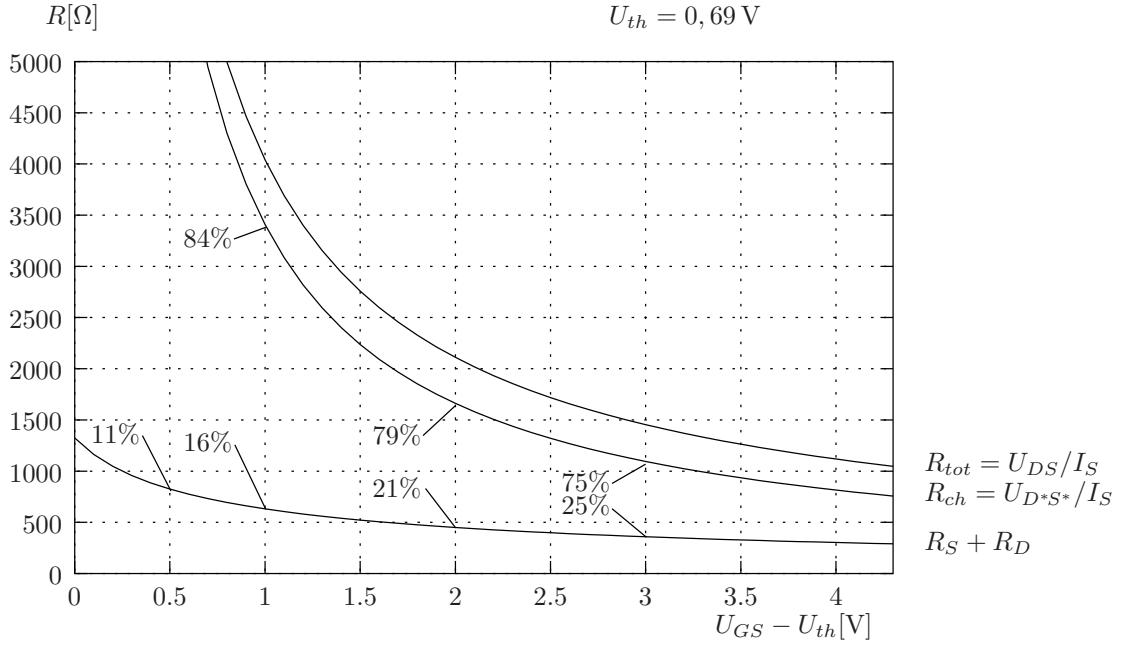

$$R_{ch} = \frac{U_{D^*S^*}}{I_D} = \frac{l_{eff}}{w \mu_n C'_{ox} \left[ (U_{GS} - U_{th}) - \frac{1}{2}(1 + \delta) U_{D^*S^*} \right]} \quad (4.2)$$

Durch Addition der seriellen Source- und Drain-Widerstände resultiert der meßbare Gesamtwiderstand des Transistors.

$$R_{tot} = R_S + R_{ch} + R_D = \frac{U_{DS}}{I_D} \quad (4.3)$$

Die Kanallänge ergibt sich aus der Länge  $l_{poly}$  des Poly-Gates abzüglich der lateralen Unterdiffusionen  $l_{ov}$ . Aufgrund der symmetrischen Fertigung hat diese source-seitig die gleiche Größe wie an der Drain.

$$l = l_{poly} - 2 l_{ov} \quad (4.4)$$

Somit gilt:

$$R_{tot} = R_S + R_D + \frac{l_{poly} - 2 l_{ov}}{w \mu_n C'_{ox} \left[ (U_{GS} - U_{th}) - \frac{1}{2}(1 + \delta) U_{D^*S^*} \right]} \quad (4.5)$$

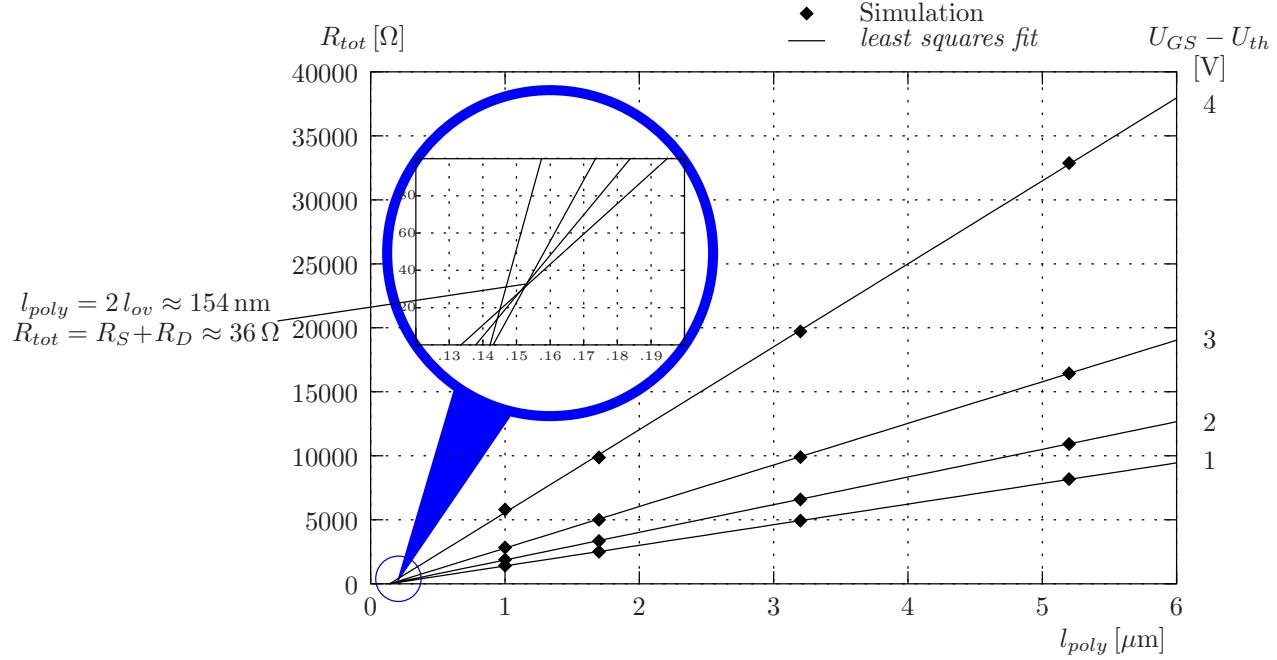

Dies ist eine lineare Gleichung mit  $l_{poly}$  als Variable. Wertet man nun verschiedene konventionelle Transistoren unterschiedlicher Größe aus und variiert dabei die Gate-Source-Spannung, so erhält man die in Abbildung 4.4 gezeigten Geraden.

Diese kreuzen sich in einem Punkt und haben eine Steigung, die mit  $U_{GS}$  wächst.

Für den extrapolierten Schnittpunkt zweier Geraden gilt:

$$\begin{aligned} R_S + R_D + \frac{l_{poly} - 2 l_{ov}}{w \mu_n C'_{ox} \left[ (U_{GS1} - U_{th}) - \frac{1}{2}(1 + \delta) U_{D^*S^*1} \right]} &= \\ R_S + R_D + \frac{l_{poly} - 2 l_{ov}}{w \mu_n C'_{ox} \left[ (U_{GS2} - U_{th}) - \frac{1}{2}(1 + \delta) U_{D^*S^*2} \right]} \end{aligned} \quad (4.6)$$

Abbildung 4.4: Schnittgeradenmethode zur Bestimmung der parasitären Widerstände mit Transistoren verschiedener Gate-Länge

Aufgrund der, abgesehen von der variablen Gate- und Kanallänge, gleichen Bauart der Transistoren gilt daher am Schnittpunkt:

$$l_{poly} = 2 l_{ov} \quad (4.7)$$

$$R_{tot} = R_S + R_D \quad (4.8)$$

Somit können auf einfache Weise die parasitären Widerstände  $R_S + R_D$  sowie die Kanallänge  $l$  extrahiert werden. Bisher wurde lediglich von HDD-Transistoren ausgegangen, bei denen die parasitären Widerstände und die Kanallänge als spannungsunabhängig angesehen werden können.

Dies ist bei LDD-Transistoren aber gerade nicht der Fall!

Folglich schneiden sich die Geraden auch nicht in einem Punkt.

Um die beschriebene Meßmethode jedoch auch für LDD-Transistoren zu verwenden, variiert man für jede Gate-Source-Spannung diese um einen geringen Wert  $\pm \Delta U_{GS}$ , für den die Widerstände als konstant angesehen werden [7]. Für die Spannungen

$$U_{GS1} = U_{GS} + \Delta U_{GS} \quad \text{und} \quad U_{GS2} = U_{GS} - \Delta U_{GS} \quad (4.9)$$

gilt somit Gleichung (4.6) näherungsweise. Bei hinreichend kleinen Spannungsvariationen konvergieren die Schnittpunkte in  $(R_S + R_D)(U_{GS})$  und  $2 l_{ov}(U_{GS})$ . Führt man

dieses Verfahren bei verschiedenen Gate-Source-Spannungen durch, so erhält man die eingangs beschriebene Spannungsabhängigkeit: Die Widerstände von Source und Drain sinken mit zunehmender Spannung, und die effektive Kanallänge

$$l_{eff}(U_{GS}) = l_{poly} - 2 l_{ov}(U_{GS}) \quad (4.10)$$

nimmt zu.

Nachteil des beschriebenen Extraktionsverfahrens ist jedoch die Notwendigkeit, mehrere Transistoren gleicher Technologie, doch mit verschiedenen Größen, vermessen zu müssen. Dieses Verfahren bietet hingegen auch einen gewaltigen Vorteil: Da sich die Vorfaktoren in Gleichung (4.6) herauskürzen, schlagen Ungenauigkeiten in der Bestimmung der Transistorweite, der Beweglichkeit und der Oxidkapazität nicht zu Buche.

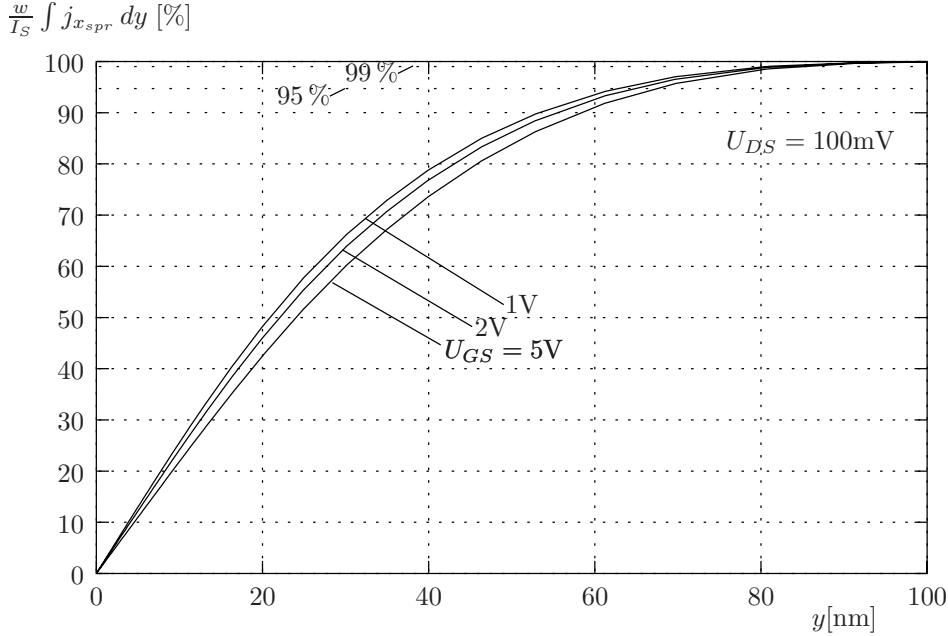

## 4.2 Messungen

Um die Abnahme der äußeren Widerstände bei steigender Gate-Source-Spannung zu verifizieren, wurden am institutseigenen Spitzen-Meßplatz Strom-Spannungs-Charakteristiken aufgenommen. Dazu wurden die Eingangskennlinien von Transistoren der C6-Technologie mit Gate-Längen zwischen 0,7 und 3 µm an offenen Teststrukturen vermessen. Zur Bestimmung der Einsatzspannung  $U_{th}$  diente das Zielstromverfahren; als Stromkriterium wurde hierfür

$$I_D = \frac{w}{l_{poly}} 2 \cdot 10^{-7} \text{ A} \quad (4.11)$$

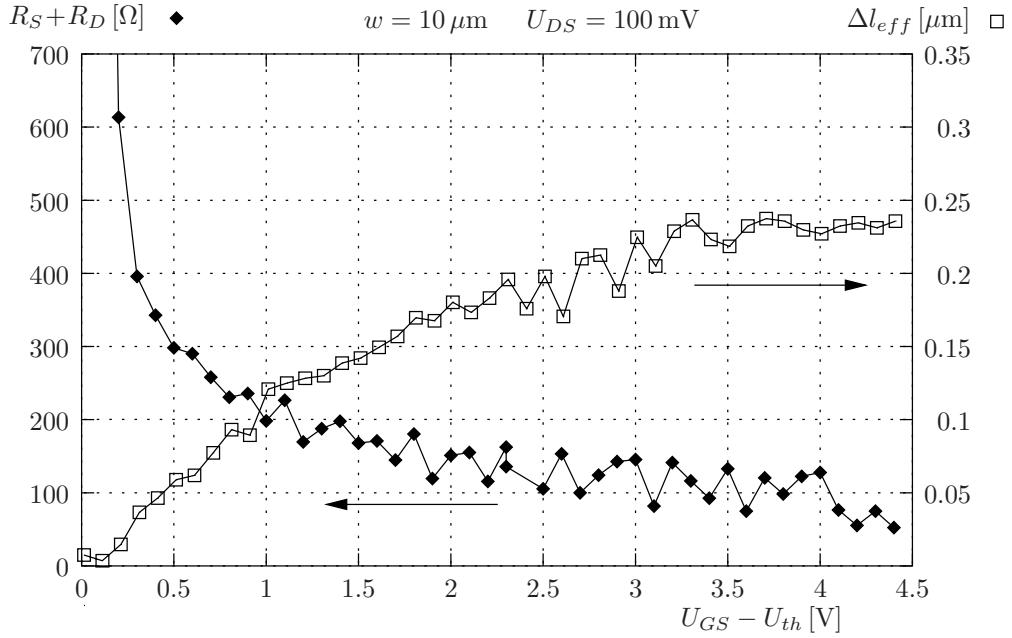

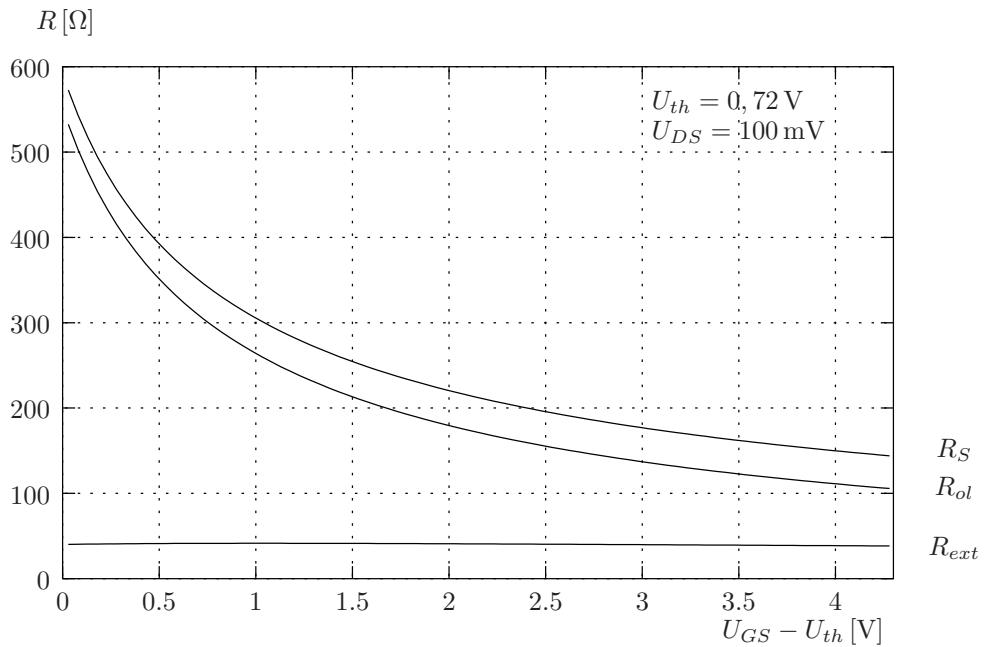

gewählt. Für die Extraktion des Widerstands  $R_S + R_D$  sowie der Änderung der effektiven Kanallänge  $\Delta l_{eff}$  nach der im vorangegangenen Kapitel beschriebenen Schnittgeradenmethode erwies sich  $\Delta U_{GS} = 50 \text{ mV}$  als sinnvoll. Die Geradengleichungen  $R_S + R_D = (R_S + R_D) (l_{poly})$  wurden für verschiedene  $U_{GS} - U_{th}$  durch *least squares fits* ermittelt. Die an den Schnittpunkten je zweier Geraden extrahierten Werte sind in Abbildung 4.5 dargestellt.

Es zeigt sich, daß die parasitären Widerstände stärker als linear mit der effektiven Gate-Spannung abfallen. Da mit zunehmender Spannung die Steigungen der Geraden immer weniger differieren, unterliegen die Schnittpunkte — und damit die extrahierten Werte — bei hohen Spannungen größeren Ungenauigkeiten. Da das Dotierungsprofil

Abbildung 4.5: Änderung der effektiven Kanallänge und  $R_S + R_D$  in Abhängigkeit von der Gate-Source-Spannung

Extraktion nach der Schnittgeradenmethode aus Messungen an Transistoren mit Gate-Längen zwischen 0,7 und 3 μm

und die Länge der Gate-Unterdiffusion der gemessenen Transistoren unbekannt waren, ist ein direkter Vergleich mit dem im folgenden angestrebten WiderstandsmodeLL nicht möglich. Auf eine exakte Fehlerbetrachtung wurde daher verzichtet; die Kurvenverläufe mögen lediglich qualitativen Zwecken dienen.

### 4.3 Widerstandsverhalten von Source und Drain

Für die Verwendung in einem Schaltungssimulator mag der im vorletzten Kapitel beschriebene Ansatz mit einer spannungsabhängigen effektiven Kanallänge nützlich sein. Jedoch führt diese Abhängigkeit bei jeder neuen Technologie zu einem veränderten Parametersatz. Insbesondere das Verlassen der geometrischen Maße, sprich: der Abstand von  $pn$ -Übergang zu  $pn$ -Übergang, ist unbefriedigend. Dieses Kapitel soll sich daher mit der reinen Widerstandsbeschreibung der Source- und Drain-Gebiete beschäftigen. Dies ist der eigentliche Impetus dieser Arbeit.

### 4.3.1 Extraktionsmethoden

Eine schwierige Frage ist die nach der Meßbarkeit der parasitären Widerstände. Diese lassen sich naturgemäß nicht direkt messen, will man den Transistor nicht zerstören, sprich: zerschneiden. Extraktionsalgorithmen sind also gefragt. Neben dem bei der Extraktion der effektiven Kanallänge vorgestellten sei noch ein anderer aufgeführt.

#### 4.3.1.1 Widerstandsextraktion durch Iterationsverfahren

Ausgangspunkt ist die vereinfachte und auf die inneren Spannungsknoten bezogene Gleichung (3.24):

$$I_D = \frac{w}{l} \mu_n C'_{ox} \left[ (U_{GS^*} - U_{th}) U_{D^*S^*} - \frac{1}{2} U_{D^*S^*}^2 \right] \quad (4.12)$$

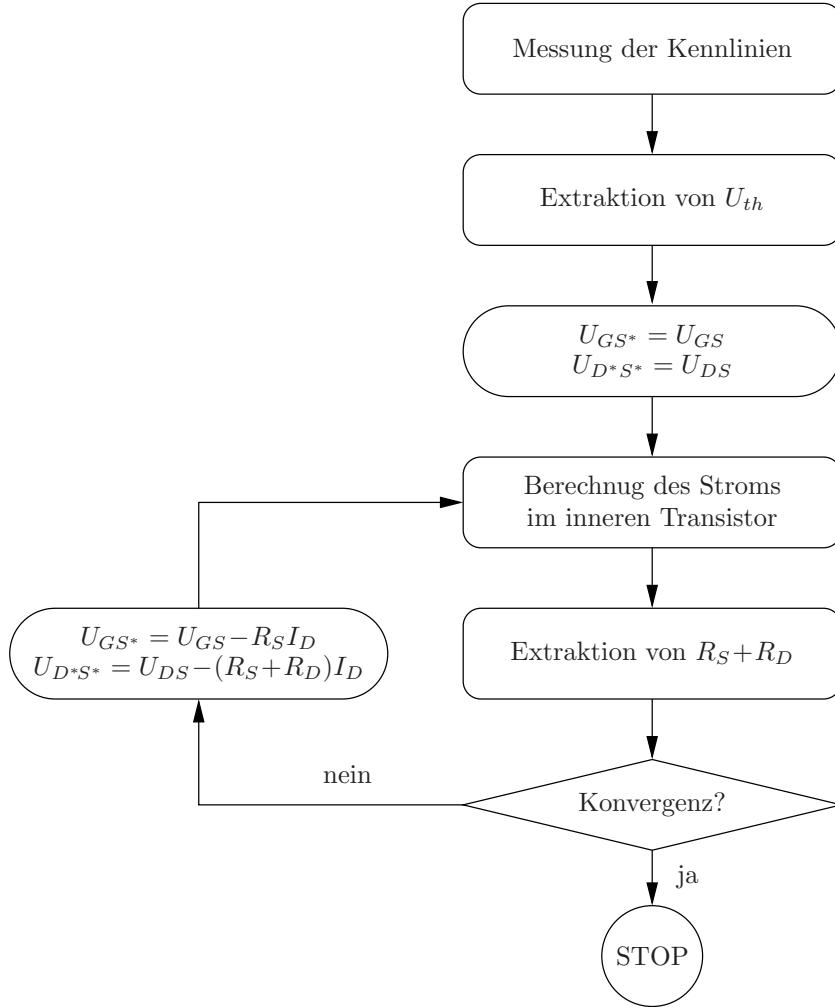

Diese Gleichung läßt sich nicht direkt auf die gemessenen Kennlinien anwenden, da man die Potentiale der inneren Knoten nicht kennt. Da eine vollständige Separation von  $R_S$  und  $R_D$  nicht möglich ist, ist man gezwungen, die Widerstände mittels Iteration zu bestimmen: Anfangs werden inneren Spannungen gleich den äußeren gesetzt. Die Einsatzspannung läßt sich aus den Kennlinien extrapoliieren. Man extrahiert für einen symmetrischen Transistor den Serienwiderstand  $R_S + R_D = 2 R_S$ . Mit dem Spannungsabfall über diese Widerstände korrigiert man die inneren Potentiale und bestimmt erneut die Widerstände. Diese Schleife wird bis zur Konvergenz durchlaufen. Abbildung 4.6 zeigt das Flußdiagramm für diesen Extraktionsalgorithmus [9].

Dieses Iterationsverfahren ist, da es für jede Gate-Source-Spannung getrennt durchgeführt werden muß, sehr rechenaufwendig.

#### 4.3.1.2 Widerstandsextraktion durch Parameteranpassung

Die inneren Spannungen lassen sich jedoch, wie bereits erwähnt, durch den Spannungsabfall über die parasitären Widerstände auf die äußeren zurückführen.

$$U_{D^*S^*} = U_{DS} - I_D (R_S + R_D) \quad (4.13)$$

$$U_{GS^*} = U_{GS} - I_D R_S \quad (4.14)$$

Abbildung 4.6: Flußdiagramm zur Extraktion von  $R_S + R_D$

Damit lässt sich für den Drain-Strom schreiben:

$$\begin{aligned}

I_D &= \frac{w}{l} \mu_n C'_{ox} \left[ \left( U_{GS*} - U_{th} \right) U_{DS*} - \frac{1}{2} U_{DS*}^2 \right] \\

&= \frac{w}{l} \mu_n C'_{ox} \left[ \left( (U_{GS} - I_D R_S) - U_{th} \right) \left( U_{DS} - I_D (R_S + R_D) \right) \right. \\

&\quad \left. - \frac{1}{2} \left( U_{DS} - I_D (R_S + R_D) \right)^2 \right]

\end{aligned} \tag{4.15}$$

Dies stellt eine im Drain-Strom quadratische Gleichung dar. Sie hat zwei Lösungen, von denen, wie in Kapitel 3 erläutert wurde, nur eine physikalisch sinnvoll ist. Eine längere Rechnung ergibt:

$$I_D = \frac{-b - \sqrt{b^2 - 4ac}}{2a} \tag{4.16}$$

mit

$$a = \frac{1}{2} (R_S + R_D) (R_S - R_D) = \frac{1}{2} (R_S^2 - R_D^2) \quad (4.17)$$

$$b = (R_S + R_D) (U_{DS} - (U_{GS} - U_{th})) - R_S - \left( \frac{w}{l} \mu_n C'_{ox} \right)^{-1} \quad (4.18)$$

$$c = (U_{GS} - U_{th}) U_{DS} - \frac{1}{2} U_{DS}^2 \quad (4.19)$$

Betrachtet man  $R_S$  und  $R_D$  als Parameter, so lässt sich obige Gleichung an gemessene Kennlinien anpassen. Oftmals verwendet man hierfür den *Levenberg-Marquardt-Algorithmus* [12, 21].

Besondere Beachtung verdient der Parameter  $b$  aus der Lösung der quadratischen Gleichung:

Die parasitären Widerstände  $R_S$  und  $R_D$  fließen hier asymmetrisch ein, was eine Separation von beiden ermöglicht. Dies ist besonders dann von Vorteil, wenn der source- und der drain-seitige Widerstand aufgrund unterschiedlicher Bemaßung oder Degradation des Transistors unterschiedliche Werte annehmen. Üblicherweise verstärkt man diesen asymmetrischen Einfluß auf das Extraktionsverfahren, indem man den Transistor auch im reverse mode, also unter Vertauschung des Source- und Drain-Anschlusses vermißt.

### 4.3.2 Modell des Source-Widerstands

In diesem ausführlichen Kapitel wird ein Modell für das Widerstandsverhalten des äußeren Transistors angestrebt. Aus besagten Gründen genügt es, das Verhalten der Source im Widerstandsbereich zu beschreiben.

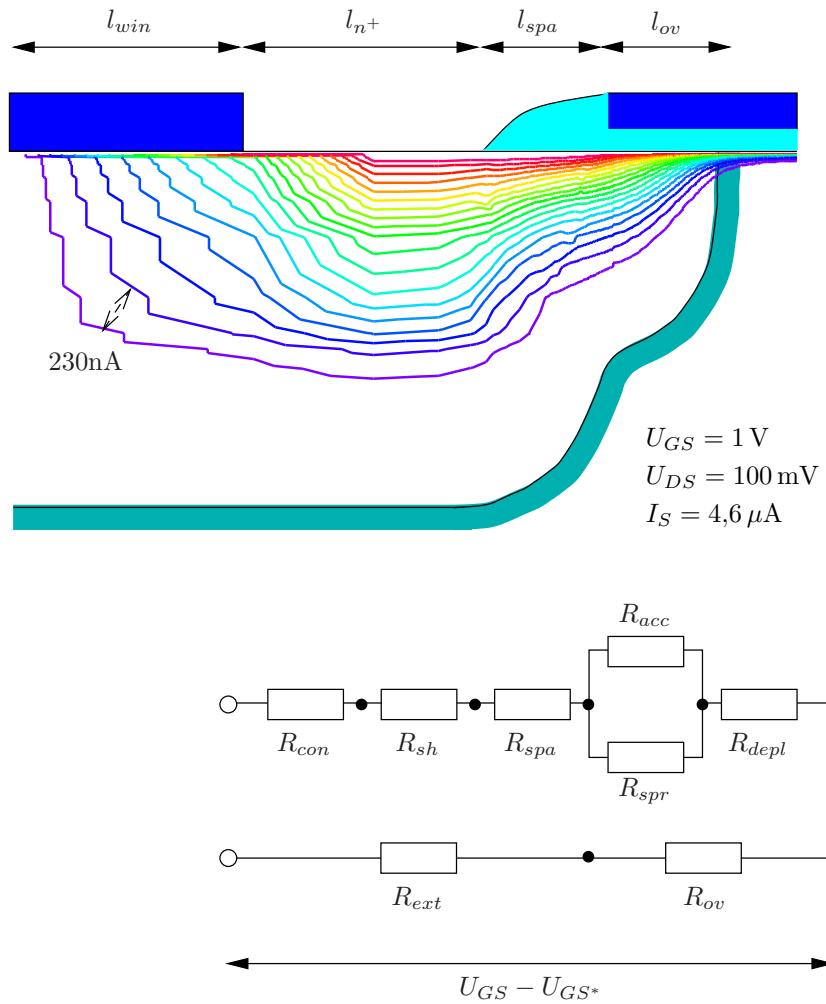

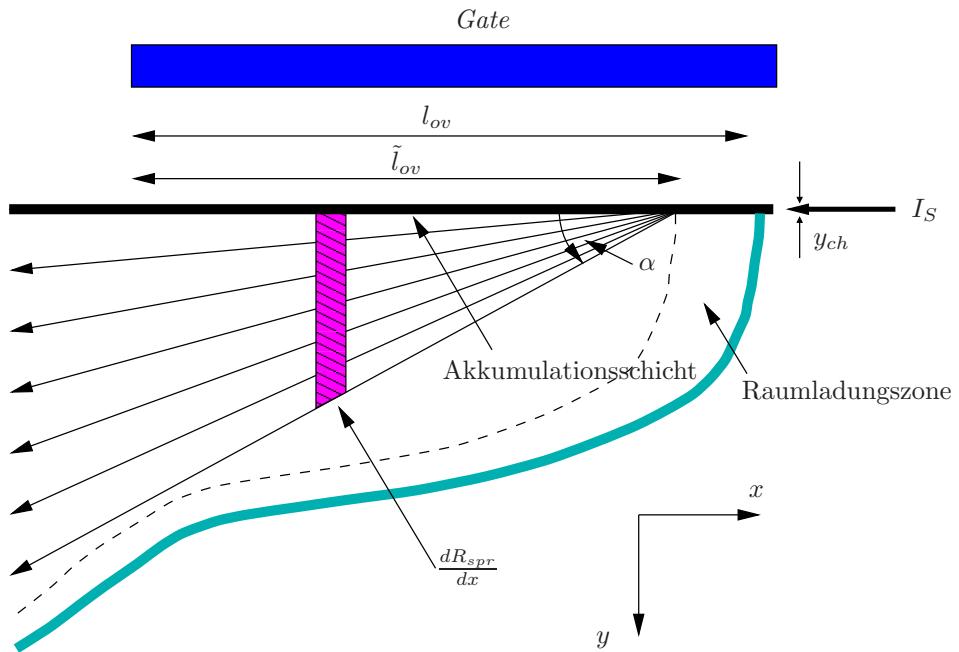

Abbildung 4.7 zeigt den typischen mit MEDICI simulierten Verlauf der Strompfade im Source-Bereich. Dies entspricht einer Vergrößerung von Abbildung 4.3.

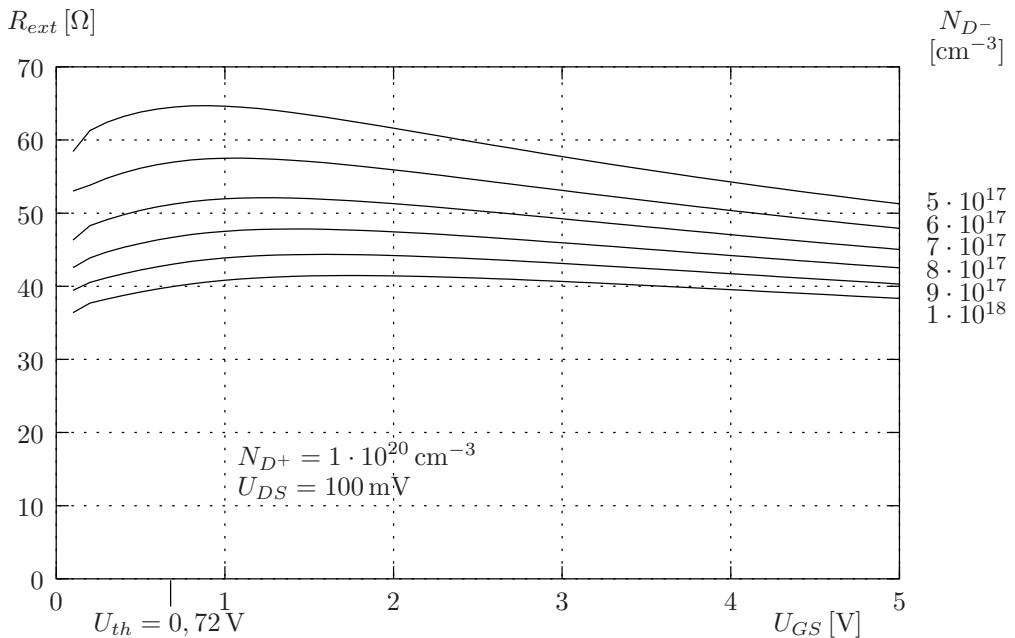

Tabelle 4.1 faßt die für die Simulation verwendeten Parameter zusammen.

Die Elektronen treten senkrecht zum äquipotentialen Source-Kontakt in das Silizium ein und durchlaufen einen Bogen in Richtung zur Drain. Der Schichtwiderstand (*sheet resistance*) im  $n^+$ -Gebiet wird annähernd parallel durchquert, ebenso das Gebiet unter dem *Spacer*. Im Überlapptgebiet verjüngt sich das Strombündel bis zum Eintritt in den Kanal auf wenige Nanometer. Dieser trichterförmig streuende Verlauf der technischen Stromrichtung führt zur Namensgebung: *Spreading-Widerstand*. Ein Großteil

Tabelle 4.1: Simulationsdaten — falls nicht anders angegeben

|                                     |             |                                                  |

|-------------------------------------|-------------|--------------------------------------------------|

| Länge des Kanals                    | $l$         | $0,8 \mu\text{m}$                                |

| Weite des Kanals                    | $w$         | $1 \mu\text{m}^{-1}$                             |

| Elektronenbeweglichkeit             | $\mu_n$     | $550 \text{ cm}^2\text{V}^{-1}\text{s}^{-1}$     |

| $n^+$ -Dotierung                    | $N_{D^+}$   | $1 \cdot 10^{-20} \text{ cm}^{-3}$               |

| $n^-$ -Dotierung                    | $N_{D^-}$   | $1 \cdot 10^{-18} \text{ cm}^{-3}$               |

| Mittlere Donatorenkonzentration     | $\bar{N}_D$ | $5,7 \cdot 10^{-17} \text{ cm}^{-3}$             |

| $p$ -Dotierung                      | $N_A$       | $1 \cdot 10^{-17} \text{ cm}^{-3}$               |

| Länge der Unterdiffusion            | $l_{ov}$    | $100 \text{ nm}$                                 |

| Oxidkapazität pro Fläche            | $C'_{ox}$   | $2,875 \cdot 10^{-15} \text{ F}\mu\text{m}^{-1}$ |

| Oxiddicke                           | $d_{ox}$    | $12 \text{ nm}$                                  |

| Länge des Oxid-Spacers              | $l_{spa}$   | $100 \text{ nm}$                                 |

| Abstand des Kontaktlochs vom Spacer | $l_{n^+}$   | $200 \text{ nm}$                                 |

der Ladungsträger fließt jedoch aufgrund der elektrostatischen Anziehung des Gates in einer Akkumulationsschicht an der Halbleiteroberfläche. Die Akkumulationsschicht und damit deren Widerstand weisen eine starke Spannungsabhängigkeit auf. Durch die Raumladungszone (*depletion region*) fließen die Elektronen in die Inversionsschicht des inneren Transistors.

Insgesamt bietet sich die in Abbildung 4.7 unten skizzierte Widerstandsverteilung an:

$$R_S = R_{con} + R_{sh} + R_{spa} + \left( \frac{1}{R_{acc} + R_{spr}} \right)^{-1} + R_{depl} \quad (4.20)$$

Besonderes Merkmal ist die Parallelschaltung des Akkumulations- und des Spreading-Widerstands.

Auf die Einführung eines Bulk-Widerstands kann aufgrund sehr geringer Substratströme verzichtet werden — sie liegen typischerweise fünf Größenordnungen unter den Drain-Strömen.

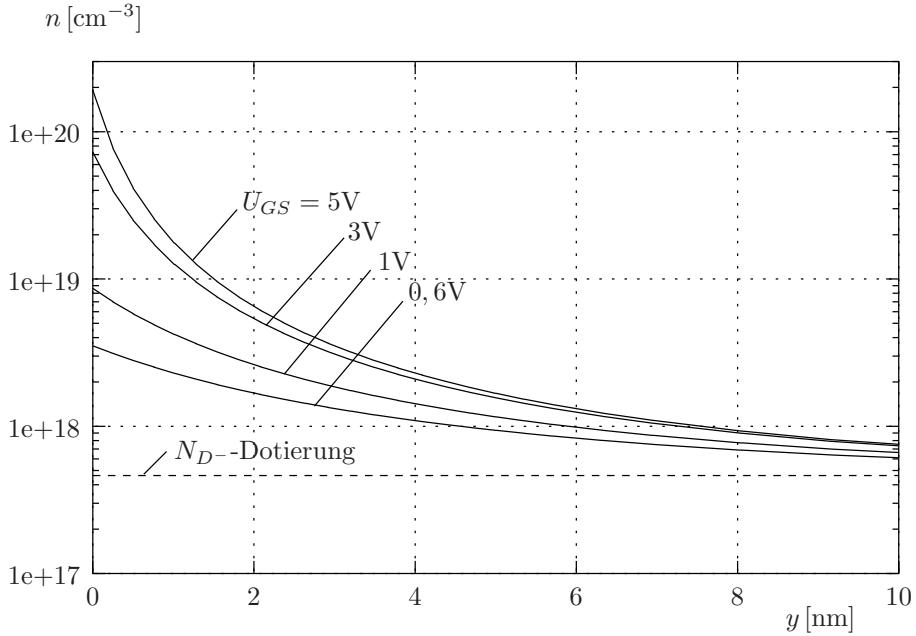

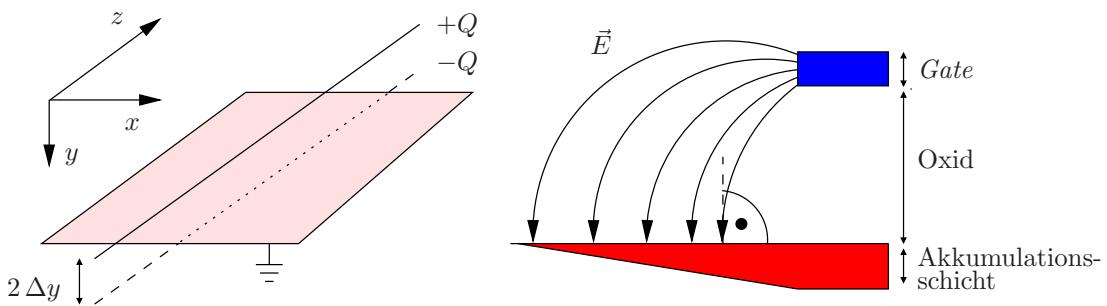

### 4.3.3 Der Akkumulationswiderstand

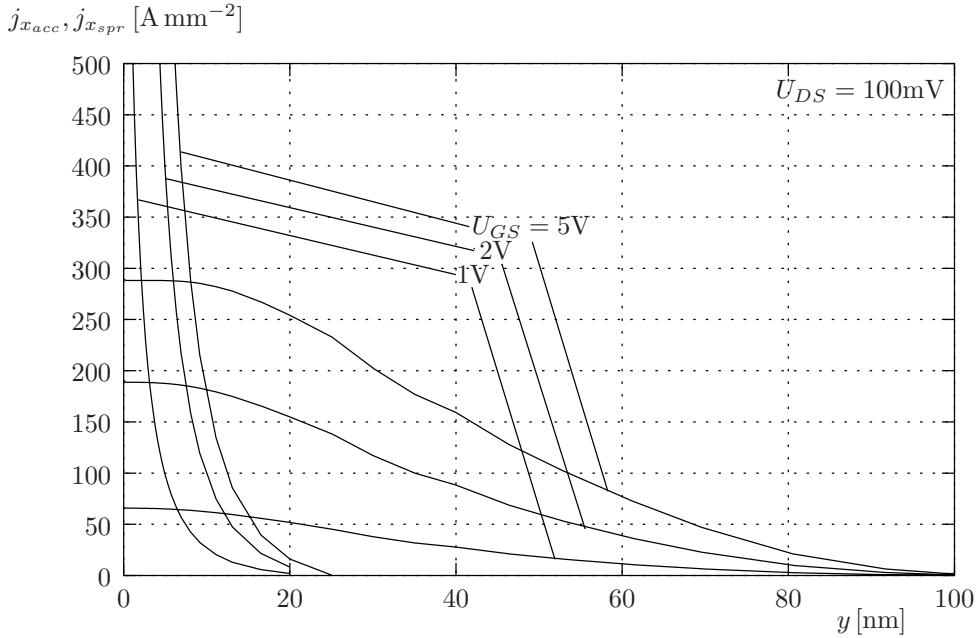

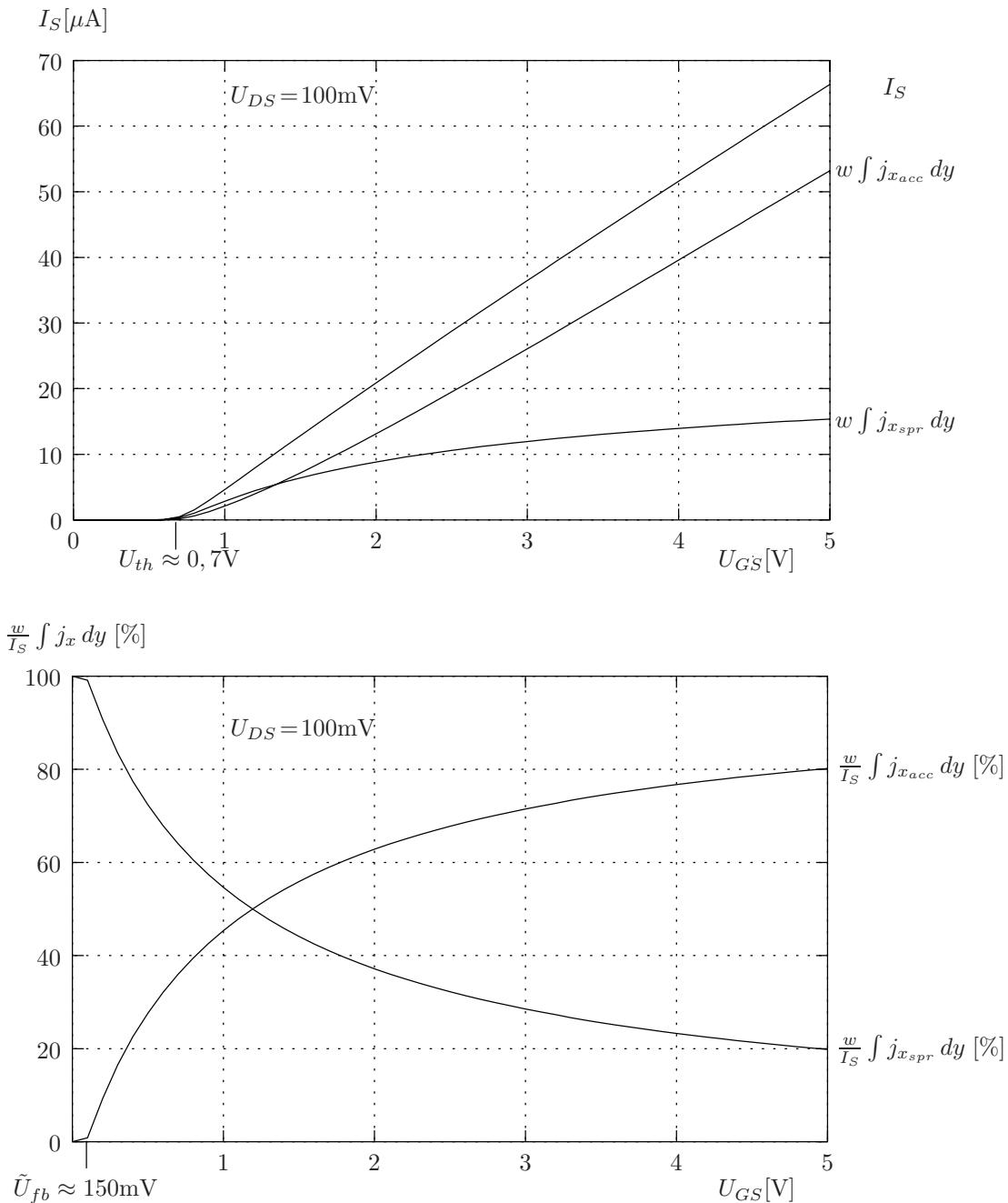

Mit zunehmender Gate-Source-Spannung sammeln sich immer mehr Elektronen in der Nähe der Halbleiteroberfläche. Abbildung 4.8 zeigt dies für einen vertikalen Schnitt in der Mitte des Überlappgebiets. Da die charakteristischen Längen im Nanometerbereich

Abbildung 4.7: Strompfade im Source-Gebiet für einen Transistor im Widerstandsbereich

Zur Modellierung verwendete Widerstandsaufteilung

liegen, was für die Simulation ein Gitter aus ungefähr 10 000 Stützstellen notwendig.

Diese Elektronenakkumulation weist wesentliche Unterschiede zur Inversionsschicht im Kanal auf:

- Während im Kanal die vertikale Elektronenverteilung (Abbildung 3.1, S. 24) nahezu exponentiell über den Ort verläuft, steigt die Dichte in der Akkumulationsschicht stärker als exponentiell an.

- Die Inversionsschicht wird begrenzt durch die sich anschließende Raumladungszone im Substrat. Eine solche bildet sich für die Akkumulationsschicht nicht aus.

Abbildung 4.8: Elektronenakkumulation an der Halbleiteroberfläche des Überlappgebiets für verschiedene Gate-Source-Spannungen

#### 4.3.3.1 Poisson-Gleichung

Eine genaue Beschreibung der Akkumulationsschicht erfordert die vertikale Lösung der Poisson-Gleichung; diese beschreibt den Zusammenhang zwischen der Ladungsdichte  $\varrho$  und dem elektrostatischen Potential  $\psi$  im Halbleiter:

$$\varepsilon_0 \varepsilon_{si} \vec{\nabla}^2 \psi = -\varrho(y) \quad (4.21)$$

Als Randbedingungen fungieren:

$$\psi = \begin{cases} \phi_s & \text{f'ur } y = 0 \\ 0 & \text{f'ur } y \rightarrow \infty \end{cases} \quad (4.22)$$

$$\frac{d\psi}{dy} = 0 \quad \text{f'ur } y \rightarrow \infty \quad (4.23)$$

Die Ladung setzt sich zusammen aus den freien Elektronen und Löchern sowie den Ionen der Donatoren und Akzeptoren.

$$\begin{aligned} \varrho(y) &= q \left[ -n(y) + p(y) + N_D^+ - N_A^- \right] \\ &\approx q \left[ -n(y) + p(y) + N_D - N_A \right] \end{aligned} \quad (4.24)$$

Im letzten Schritt wurde — wie schon in den vorhergehenden Kapiteln — vollständige Ionisierung der Dotieratome angenommen.

Im  $n$ -dotierten Überlappgebiet werden die Majoritätsträger durch Gleichung (2.11)

$$n(y) = n_i e^{-\frac{\phi_F - \psi(y)}{\phi_t}} \quad (4.25)$$

und die Minoritätsträger durch Gleichung (2.12)

$$p(y) = n_i e^{\frac{\phi_F - \psi(y)}{\phi_t}} \quad (4.26)$$

beschrieben.

Der Vollständigkeit halber seien nochmals die Definitionen für die Intrinsic-Dichte, das Fermi-Potential und die Thermospannung aufgeführt.

$$n_i = \sqrt{N_D N_A} \quad (4.27)$$

$$\phi_F = -\frac{E_F - E_i}{q} = -\frac{k T}{q} \ln \frac{N_D}{n_i} \quad (4.28)$$

$$\phi_t = \frac{k T}{q} \stackrel{(T=300\text{K})}{\approx} 26\text{mV} \quad (4.29)$$

In der Tiefe des Source-Gebiets herrscht Ladungsneutralität; dort gilt also:

$$\begin{aligned} N_D - N_A &= -n(y \rightarrow \infty) + p(y \rightarrow \infty) \\ &\stackrel{4.25, 4.26}{=} n_i e^{-\frac{\phi_F - \psi(y \rightarrow \infty)}{\phi_t}} - n_i e^{\frac{\phi_F - \psi(y \rightarrow \infty)}{\phi_t}} \\ &\stackrel{\psi(y \rightarrow \infty)=0}{=} n_i \left( e^{-\frac{\phi_F}{\phi_t}} - e^{\frac{\phi_F}{\phi_t}} \right) \\ &= -2 n_i \sinh \left( \frac{\phi_F}{\phi_t} \right) \end{aligned} \quad (4.30)$$

Setzt man (4.25), (4.26) und (4.30) in Gleichung (4.24) ein, so lässt sich die Ladungsträgerdichte über die Potentiale beschreiben:

$$\begin{aligned} \varrho(y) = \varrho(\psi(y)) &= q \left[ -n_i e^{-\frac{\phi_F - \psi(y)}{\phi_t}} + n_i e^{\frac{\phi_F - \psi(y)}{\phi_t}} + n_i e^{-\frac{\phi_F}{\phi_t}} - n_i e^{\frac{\phi_F}{\phi_t}} \right] \\ &= 2 q n_i \left[ \sinh \left( \frac{\phi_F - \psi(y)}{\phi_t} \right) - \sinh \left( \frac{\phi_F}{\phi_t} \right) \right] \end{aligned} \quad (4.31)$$

Die Poisson-Gleichung (4.21) nimmt somit die Form

$$\vec{\nabla}^2 \psi = \frac{d^2 \psi}{dy^2} = -\frac{\varrho(y)}{\varepsilon_0 \varepsilon_{si}} = -\frac{2 q n_i}{\varepsilon_0 \varepsilon_{si}} \left[ \sinh \left( \frac{\phi_F - \psi(y)}{\phi_t} \right) - \sinh \left( \frac{\phi_F}{\phi_t} \right) \right] \quad (4.32)$$

an. Dies ist eine gewöhnliche Differentialgleichung zweiter Ordnung für das Halbleiterpotential  $\psi$ .

Mit der Operatoridentität

$$2 \frac{d\psi}{dy} \frac{d^2\psi}{dy^2} = \frac{d}{dy} \left( \frac{d\psi}{dy} \right)^2 \quad (4.33)$$

und der elektrischen Feldstärke  $E(y) = -d\psi/dy$  ergibt sich aus Gleichung (4.32):

$$\frac{d}{dy} E^2(y) = -\frac{4 q n_i}{\varepsilon_0 \varepsilon_{si}} \frac{d\psi}{dy} \left[ \sinh \left( \frac{\phi_F - \psi(y)}{\phi_t} \right) - \sinh \left( \frac{\phi_F}{\phi_t} \right) \right] \quad (4.34)$$

Trennung der Variablen und Integration über  $y$  mit den Randbedingungen (4.22) und (4.23) führt zu

$$\int_{E^2(y)}^{E^2(y \rightarrow \infty) = 0} dE^2(y) = -\frac{4 q n_i}{\varepsilon_0 \varepsilon_{si}} \int_{\psi(y)}^{\psi(y \rightarrow \infty) = 0} \sinh \left( \frac{\phi_F - \psi(y)}{\phi_t} \right) - \sinh \left( \frac{\phi_F}{\phi_t} \right) d\psi \quad (4.35)$$

und nach einigem Rechenaufwand zu:

$$\begin{aligned} E^2(y) &= \frac{2 q n_i}{\varepsilon_0 \varepsilon_{si}} \left[ e^{\frac{\phi_F}{\phi_t}} \left( \phi_t e^{-\frac{\psi(y)}{\phi_t}} + \psi(y) - \phi_t \right) + e^{-\frac{\phi_F}{\phi_t}} \left( \phi_t e^{\frac{\psi(y)}{\phi_t}} - \psi(y) - \phi_t \right) \right] \\ &\stackrel{(4.30)}{=} \frac{2 q N_D}{\varepsilon_0 \varepsilon_{si}} \left[ \frac{N_A}{N_D} \left( \phi_t e^{-\frac{\psi(y)}{\phi_t}} + \psi(y) - \phi_t \right) + \phi_t e^{\frac{\psi(y)}{\phi_t}} - \psi(y) - \phi_t \right] \end{aligned} \quad (4.36)$$

Im Überlappgebiet übertrifft die Donatorenkonzentration die der Grunddotierung bei weitem, so daß der Faktor  $N_A/N_D$  vernachlässigbar klein wird.

Da nur positive Gate-Source-Spannungen von Interesse sein sollen, das Feld also vertikal in den Halbleiter gerichtet ist, folgt:

$$E(y) = \sqrt{\frac{2 q N_D}{\varepsilon_0 \varepsilon_{si}} \left( \phi_t e^{\frac{\psi(y)}{\phi_t}} - \psi(y) - \phi_t \right)} \quad (4.37)$$

Die zweite Integration der Poisson-Gleichung

$$-\int_0^y E(y) dy = \int_{\psi(y=0)=\phi_s}^{\psi} d\psi \quad (4.38)$$

ist auch nach Trennen der Variablen

$$\int_0^y \sqrt{\frac{2 q N_D}{\varepsilon_0 \varepsilon_{si}}} dy = \int_{\psi(y=0)=\phi_s}^{\psi} \frac{d\psi}{\sqrt{\phi_t e^{\frac{\psi(y)}{\phi_t}} - \psi(y) - \phi_t}} \quad (4.39)$$

nicht allgemein möglich. Somit existiert auch keine geschlossene Darstellung von  $\psi(y)$  in Abhängigkeit von der Gate-Source-Spannung. Mithin ist auch die Bestimmung der örtlichen Verteilung der Ladungsträgerdichte (4.32) nur numerisch — wie in Abbildung 4.8 — möglich.

Daher wird nun eine einfachere Modellierung des Akkumulationswiderstandes angestrebt.

Der Widerstand pro lateraler Längeneinheit ist indirekt proportional zur Leitfähigkeit des Halbleiters und der vom Strom durchflossenen Fläche.

$$\frac{dR_{acc}}{dx} = \frac{1}{\int_{z=0}^{z=w} \int_{y=0}^{y \rightarrow \infty} \sigma(y) dy dz} \quad (4.40)$$

Die Leitfähigkeit  $\sigma$  ist der Absolutwert des Produkts aus der Ladungsträgerdichte  $\varrho$  und deren Beweglichkeit  $\mu$ . Sie kann, abgesehen von Randbereichen, als über die Weite  $w$  des Transistors konstant angenommen werden.

Wegen der Gültigkeit von

$$\frac{|\varrho(y)|}{q} \approx n'(y) \stackrel{(def)}{=} n(y) - N_D \gg N_A - p \quad (4.41)$$

im Überlappgebiet lässt sich unter Verwendung der Überschuß-Elektronendichte  $n'$  und der Nomenklatur aus Abbildung 4.7 (S. 45) weiterführen:

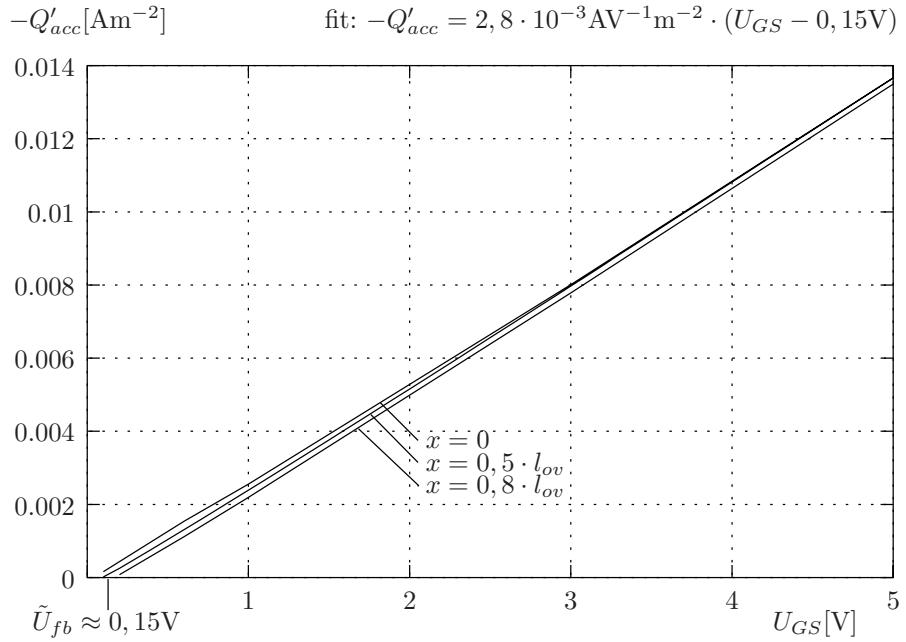

$$\begin{aligned} R_{acc} &= \int_{x=0}^{x=\tilde{l}_{ov}} \frac{1}{w \int_{y=0}^{y \rightarrow \infty} \mu_n |\varrho(y)| dy} dx = \int_{x=0}^{x=\tilde{l}_{ov}} \frac{1}{w \mu_n \int_{y=0}^{y \rightarrow \infty} qn'(y) dy} dx \\ &= \int_{x=0}^{x=\tilde{l}_{ov}} \frac{1}{w \mu_n (-Q'_{acc})} dx = -\frac{\tilde{l}_{ov}}{w \mu_n Q'_{acc}} \end{aligned} \quad (4.42)$$

Besonders erwähnenswert ist hierbei die Tatsache, daß nicht die im vorigen Kapitel angestrebte lokale Verteilung der Überschuß-Elektronen von Bedeutung ist, sondern lediglich deren integrale Summe:

$$Q'_{acc} = -q \int_{y=0}^{y \rightarrow \infty} n'(y) dy \quad (4.43)$$

Die Akkumulationsladung pro Fläche  $Q'_{acc}$  erhält man unter Verwendung des Gaußschen Satzes [8].

$$Q'_{acc} = \frac{\varepsilon_0 \varepsilon_{si}}{A} \oint \vec{E} d\vec{A} \quad (4.44)$$

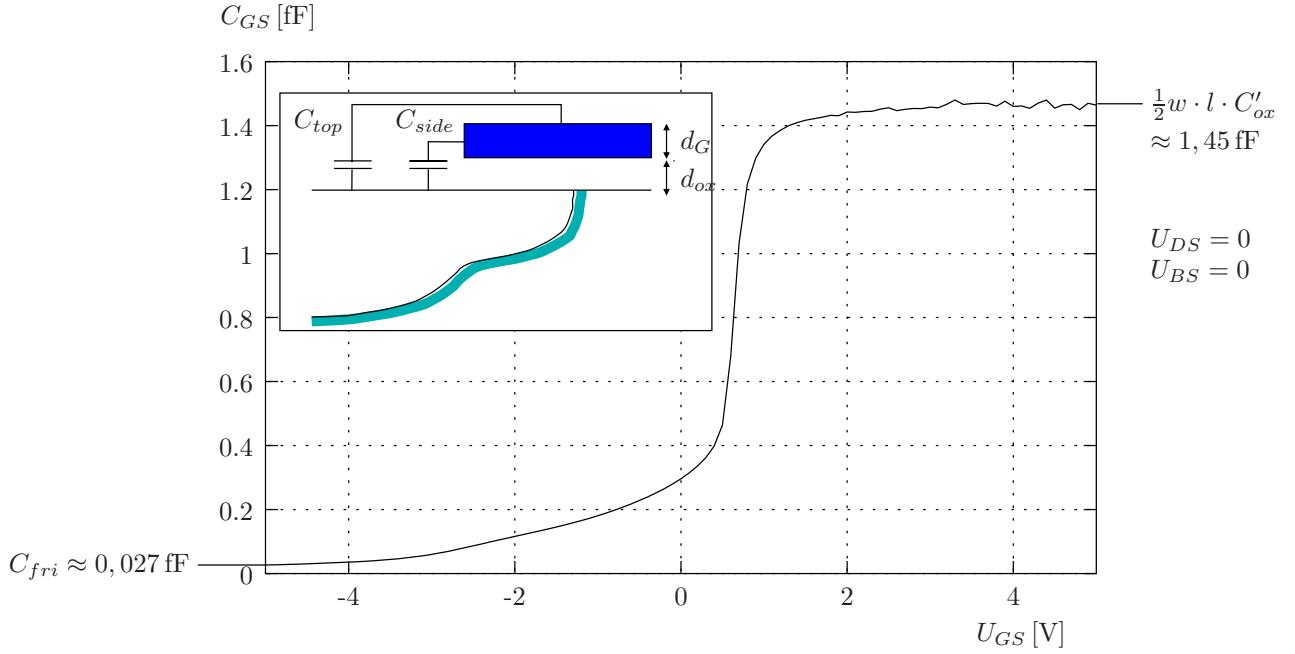

Somit lässt sich — mit der Randbedingung einer im Unendlichen verschwindenden Feldstärke — mit Gleichung (4.37) die Ladung pro Flächeneinheit in Abhängigkeit vom Oberflächenpotential  $\phi_s = \psi(y=0)$  berechnen.